提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、pandas是什么?

-

二、使用步骤

- 1.引入库

- 2.读入数据

- 总结

前言

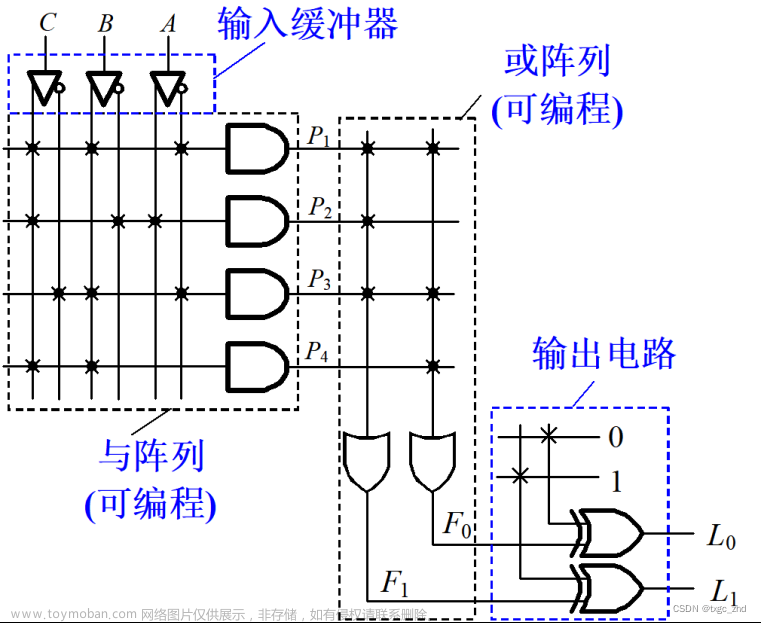

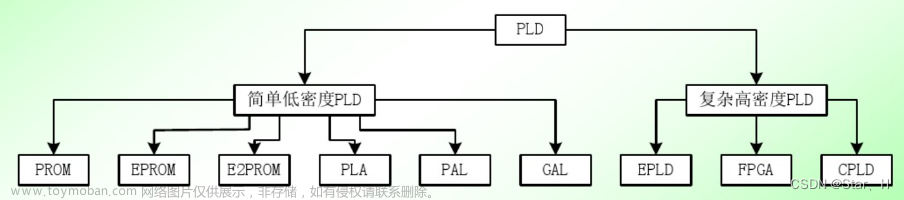

1.根据PLD器件单片集成度的高低,可将PLD分为低密度可编程逻辑器件和高密度可编程逻辑器件。

2.按器件结构类型划分

目前常用的可编程逻辑器件都是从“与-或阵列”和“门阵列”两类基本结构发展起来的,所以可编程逻辑器件从结构上可分为两大类:

(1)乘积项结构器件。其基本结构为“与-或阵列”的器件。简单PLD、EPLD和CPLD都属于此类器件。

(2)查找表结构器件。其基本结构类类似于“门阵列”的器件,它由简单的查找表组成可编程逻辑门,再构成阵列形式。大多数FPGA属于此类器件

3.掉电后

(1)CPLD。掉电后重新上电还能保持编程信息的器件。

(2)FPGA。掉电后不能保持编程信息的器件。

FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的。

一、存储器和寄存器的区别?

存储器和寄存器的区别是:

1、存储器功能:存放指令和数据,并能由中央处理器(CPU)直接随机存取。

2、寄存器功能:可将寄存器内的数据执行算术及逻辑运算;存于寄存器内的地址可用来指向内存的某个位置,即寻址;可以用来读写数据到电脑的周边设备。

3、寄存器的速度比主存储器的速度要快很多,由于寄存器的容量有限,所以将不需要操作的数据存放在主存储器中,主存储器中的数据必须放入寄存器材能够进行操作。

4、简单地说:寄存器是操作数据的地方,存储器是存放数据的地方。

5、寄存器一般是指由基本的RS触发器结构衍生出来的D触发,就是一些与非门构成的结构,一般整合在CPU内,其读写速度跟CPU的运行速度基本匹配,但因为性能优越,所以造价昂贵,一般好的CPU也就只有几MB的级缓存,级缓存更小。

二、移位寄存器

移位寄存器是一种时序逻辑电路,能够存储和传输数据。它们由触发器组成,这些触发器的连接方式使得一个触发器的输出可以作为另一个触发器的输入,具体取决于所创建的移位寄存器的类型。移位寄存器基本上是一种能够传输(“移位”)数据的寄存器。寄存器通常是存储设备,它们是通过将特定数量的触发器串联在一起而创建的,并且寄存器可以存储的数据量(位数)始终与触发器的数量成正比,因为每个触发器一次只能存储一个bit。当寄存器中的触发器以这样的方式连接时,一个触发器的输出成为另一个触发器的输入,就会创建一个移位寄存器

触发器是具有类似于闩锁操作的设备,被称为双稳态电路,有两个稳定的状态,即0或1,并且能够以bit为单位存储数据。每当D触发器的时钟发生变化时(上升沿或下降沿,取决于触发器的规格)。输出“Q”处的数据与输入“D”处的数据相同。触发器的输出“Q”将保持在该值,直到下一个时钟周期,然后它将再次更改为输入处的值(1或0)。

1.串行输入—串行输出移位寄存器

串行输入 – 串行输出移位寄存器,它以串行方式(每个时钟周期一位)流式传入数据,并以相同的方式逐个流出数据。

文章来源:https://www.toymoban.com/news/detail-827386.html

一个简单的4位串行输入 – 串行输出移位寄存器如上所示,寄存器由4个触发器组成,其工作原理如下所述;

启动时,首先复位移位寄存器,所有触发器的输出为零,然后将输入数据串行施加到输入端,一次一位。

下图显示了数据1101如何从串行输入—并行输出

第一个周期

第二个周期

第三个周期

第四个周期

2.串行输入—并行输出移位寄存器

这类移位寄存器用于将数据从串行转换为并行。每个时钟周期的数据一个接一个地输入,这意味着当数据被读入时,每个读入位在其各自的输出线上同时输出(Q0 – Q3,对于如下所示的4位移位寄存器)。4位串行输入—并行输出移位寄存器如下图所示。

4 人赞同了该文章

什么是移位寄存器:

移位寄存器是一种时序逻辑电路,能够存储和传输数据。它们由触发器组成,这些触发器的连接方式使得一个触发器的输出可以作为另一个触发器的输入,具体取决于所创建的移位寄存器的类型。移位寄存器基本上是一种能够传输(“移位”)数据的寄存器。寄存器通常是存储设备,它们是通过将特定数量的触发器串联在一起而创建的,并且寄存器可以存储的数据量(位数)始终与触发器的数量成正比,因为每个触发器一次只能存储一个bit。当寄存器中的触发器以这样的方式连接时,一个触发器的输出成为另一个触发器的输入,就会创建一个移位寄存器。

移位寄存器

触发器是具有类似于闩锁操作的设备,被称为双稳态电路,有两个稳定的状态,即0或1,并且能够以bit为单位存储数据。每当D触发器的时钟发生变化时(上升沿或下降沿,取决于触发器的规格)。输出“Q”处的数据与输入“D”处的数据相同。触发器的输出“Q”将保持在该值,直到下一个时钟周期,然后它将再次更改为输入处的值(1或0)。

D触发器

D触发器功能

数字电路中的寄存器类型

移位寄存器主要根据其工作模式(串行或并行)分为几类。下面列出了几种基本移位寄存器,尽管其中一些可以根据数据流的方向进一步划分,右移或者左移。

1. 串口输入—串口移位寄存器 (SISO)2. 串行输入—并行输出移位寄存器 (SIPO)3. 并联输入—并联输出移位寄存器 (PIPO)4. 并联输入—串行移位寄存器 (PISO)5. 双向移位寄存器

1. 串行输入—串行输出移位寄存器

串行输入 – 串行输出移位寄存器,它以串行方式(每个时钟周期一位)流式传入数据,并以相同的方式逐个流出数据。

移位寄存器

一个简单的4位串行输入 – 串行输出移位寄存器如上所示,寄存器由4个触发器组成,其工作原理如下所述;

启动时,首先复位移位寄存器,所有触发器的输出为零,然后将输入数据串行施加到输入端,一次一位。

下图显示了数据1101如何从串行输入—并行输出

第一个周期

第二个周期

第三个周期

第四个周期

2. 串行输入—并行输出移位寄存器

这类移位寄存器用于将数据从串行转换为并行。每个时钟周期的数据一个接一个地输入,这意味着当数据被读入时,每个读入位在其各自的输出线上同时输出(Q0 – Q3,对于如下所示的4位移位寄存器)。4位串行输入—并行输出移位寄存器如下图所示。

下图显示了数据1001如何从串行输入-并行输出

3. 并行输入—串行输出移位寄存器

在并行输入—串行输出移位寄存器中,数据是并行输入的,例如如下所示的4位寄存器。该寄存器可用于存储和移位4bit数据,WS控制控制移位寄存器的工作模式(写入/移位)。当WS控制线为低电平(写入模式)时,数据可以通过D0到D3写入寄存器。为了连续地将数据移出,WS控制线被置于HIGH(移位模式),然后寄存器在时钟输入时将数据移出。

4. 并行输入—并行输出移位寄存器

对于并联输入– 并联输出移位寄存器,并行输出端的输出数据在输入数据输入时同时出现。当器件计时时,从D0到D3的每个输入引脚的输入数据同时输入,同时,从每个输入的数据在相应的输出(从Q0到Q3)处输出。

三、查找表LUT

为了解决传统逻辑电路的的问题,在FPGA中,使用LUT来实现组合逻辑电路的功能。 LUT 本质上是一个SRAM,里面存储的数据类似于真值表,它将上例中的逻辑与门和或门分别使用两张类似于真值表的东西代替,LUT中保存着输入变量和经过逻辑门后输出变量的所有结果。在实现上,它将输入数据作为SRAM的地址,然后通过该地址找到对应的值,将该值作为结果输出。比如上例中的与门,在该与门对应的LUT中,地址为0、0的存储单元中保存着0,地址为0、1的存储单元中保存着0,地址为1、0的存储单元中保存着0,地址为1、1的存储单元中保存着1;当输入变量为0、1时,就会直接将LUT中地址为0、1的存储单元中的0输出。 上例中查找表构成的电路:

该组合逻辑的真值表:

如果使用传统的数字电路的方法,则要实现该组合逻辑电路,需要经过下面几个过程:

通过真值表得到输入和输出之间的逻辑关系;通过化简卡诺图得到描述输入输出变量关系的逻辑表达式;通过逻辑电路实现逻辑表达式。

众所周知,在设计时序电路时,时序电路的工作性能极为重要。然而,采用传统逻辑门电路实现逻辑关系的方法存在一些严重的缺点:

输入变量从通过逻辑电路到输出变量,存在一定的延迟,该延迟的大小和逻辑电路的复杂程度密切相关。逻辑电路越复杂,延迟越大,因此,延迟是不确定的;延时的倒数是频率,频率和时序电路的工作速率密切相关。因为延迟不确定,所以频率也不确定,这将严重影响整个电路的工作性能;逻辑电路的复杂程度和输入逻辑变量的个数、逻辑门的个数有关。因此输入逻辑变量越多,逻辑电路就越复杂。

为了解决传统逻辑电路的的问题,在FPGA中,使用LUT来实现组合逻辑电路的功能。

LUT 本质上是一个SRAM,里面存储的数据类似于真值表,它将上例中的逻辑与门和或门分别使用两张类似于真值表的东西代替,LUT中保存着输入变量和经过逻辑门后输出变量的所有结果。在实现上,它将输入数据作为SRAM的地址,然后通过该地址找到对应的值,将该值作为结果输出。比如上例中的与门,在该与门对应的LUT中,地址为0、0的存储单元中保存着0,地址为0、1的存储单元中保存着0,地址为1、0的存储单元中保存着0,地址为1、1的存储单元中保存着1;当输入变量为0、1时,就会直接将LUT中地址为0、1的存储单元中的0输出。

上例中查找表构成的电路:

总结

使用LUT代替传统的逻辑门实现组合逻辑的优点:文章来源地址https://www.toymoban.com/news/detail-827386.html

- 通过LUT代替组合逻辑,而LUT中的值只和输入有关,因此组合逻辑的功能由输入决定,不在和复杂度有关;

- LUT实现的组合逻辑的延迟是固定的。

到了这里,关于FPGA的可编程逻辑单元(LUT和寄存器)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!