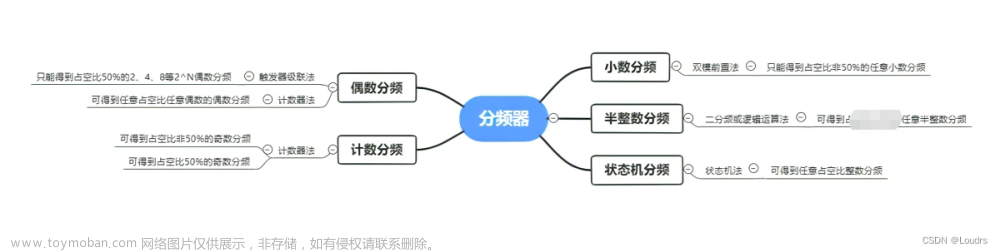

在数字系统的设计中经常会碰到需要使用多个时钟的情况。时钟信号的产生通常具有两种方法,一种是使用PLL(Phase Locked Loop,锁相环),可生成倍频、分频信号;另一种则是使用硬件描述语言构建一个分频电路。

分频器的设计通常分为以下三类:奇数分频器、偶数分频器及小数分频器。

1.偶数分频

只是注意时钟翻转的条件是(N/2)还是(N/2)-1,非阻塞赋值在下一个时钟才会更新值

(1)请使用D触发器设计一个同时输出2/4/8分频的50%占空比的时钟分频器,注意rst为低电平复位

`timescale 1ns/1ns

module even_div

(

input wire rst,

input wire clk_in,

output wire clk_out2,

output wire clk_out4,

output wire clk_out8

);

//*************code***********//

reg clk_out2_r;

reg clk_out4_r;

reg clk_out8_r;

//2分频

always@(posedge clk_in or negedge rst)begin

if(!rst)begin

clk_out2_r <= 0;

end

else begin

clk_out2_r <= ~clk_out2_r;

end

end

//4分频

always@(posedge clk_out2 or negedge rst)begin

if(!rst)begin

clk_out4_r <= 0;

end

else begin

clk_out4_r <= ~clk_out4_r;

end

end

//8分频

always@(posedge clk_out4 or negedge rst)begin

if(!rst)begin

clk_out8_r <= 0;

end

else begin

clk_out8_r <= ~clk_out8_r;

end

end

assign clk_out2 = clk_out2_r;

assign clk_out4 = clk_out4_r;

assign clk_out8 = clk_out8_r;

//*************code***********//

endmodule(2)8分频

//8分频电路设计

module divider_8 //模块名

(

input sys_clk, //时钟(设定为 50MHz)

input sys_rst_n, //复位信号(n 表示低电平有效)

output reg clk_8 //输出8分频信号

);

reg [1:0] cnt; //reg 定义

//计数模块

//从0计数到3共计4个时钟周期

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

cnt <= 2'd0; //复位清零

else if(cnt == 2'd3) //从0开始计数,所以需要 -1

cnt <= 2'd0; //计满则清零

else

cnt <= cnt + 2'd1; //没记满就一直计数

end

//8分频时钟输出模块

//满足计数条件则对8分频时钟进行反转

//8分频时钟每隔4个周期反转一次,所以8分频的周期即为8个时钟周期

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

clk_8 <= 1'b0; //复位清零

else if(cnt == 2'd3) //记满4个时钟周期

clk_8 <= ~clk_8; //计满则输出反转

else

clk_8 <= clk_8; //没记满就保持原来状态

end

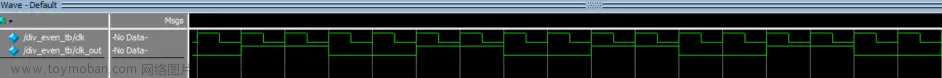

endmoduletestbench

`timescale 1ns/1ns //时间刻度:单位1ns,精度1ns

module tb_divider_8(); //仿真模块

//输入reg 定义

reg sys_clk;

reg sys_rst_n;

//输出wire定义

wire clk_8;

//设置初始化条件

initial begin

sys_clk = 1'b0; //初始时钟为0

sys_rst_n <= 1'b0; //初始复位为0

#10 //10个时间单位后

sys_rst_n <= 1'b1; //拉高复位(此时复位无效)

end

//always代表重复进行,#10代表每10个时间单位

//每10个时间单位反转时钟,即时钟周期为20个时间单位(20ns)

always #10 sys_clk = ~sys_clk;

//例化被测试模块

divider_8 divider_8_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.clk_8 (clk_8 )

);

endmodule2.奇数分频

奇数分频比偶数分频复杂一些,当不要求分频的占空比时,对输入时钟clk上升沿计数,可以设置两个计数的翻转点,一个是(N-1)/2,一个是(N-1),计数到(N-1)时输出时钟翻转且将计数器清零,假设计数器计数0~(N-1)/2区间输出低电平,则输出时钟的低电平有(N-1)/2 + 1个clk周期,高电平的计数是(N-1)/2+1 ~ (N-1),共(N-1)/2个clk周期,可见不是50%占空比。

当要求占空比为50%时,对输入时钟clk的上升沿和下降沿分别计数,根据两个计数器得到两个错位输出的时钟,将两个时钟做“或”运算,可以弥补相差的时钟,达到50%占空比。文章来源:https://www.toymoban.com/news/detail-828356.html

文章来源地址https://www.toymoban.com/news/detail-828356.html

文章来源地址https://www.toymoban.com/news/detail-828356.html

/********************************************

计数器实现 7 分频

*********************************************/

module Odd_Divider(

inputclk,

inputrst_n,

outputclk_divider

);

reg [2:0] count_p; //上升沿计数

reg [2:0] count_n; //下降沿计数

reg clk_p; //上升沿分频

reg clk_n; //下降沿分频

//上升沿计数

always @ ( posedge clk or negedge rst_n )

begin

if(!rst_n )

count_p<= 3'b0;

elseif( count_p == 3'd6 )

count_p<= 3'b0;

else

count_p<= count_p + 1'b1;

end

//上升沿分频

always @ ( posedge clk or negedge rst_n )

begin

if(!rst_n ) begin

clk_p<= 1'b0;

end

elsebegin

if(count_p == 3'd3 || count_p == 3'd6 ) begin

clk_p<= ~clk_p;

end

end

end

//下降沿计数

always @ ( negedge clk or negedge rst_n )

begin

if(!rst_n )

count_n<= 3'b0;

elseif( count_n == 3'd6 )

count_n<= 3'b0;

else

count_n<= count_n + 1'b1;

end

//下降沿分频

always @ ( negedge clk or negedge rst_n )

begin

if(!rst_n ) begin

clk_n<= 1'b0;

end

elsebegin

if(count_n == 3'd3 || count_n == 3'd6 ) begin

clk_n<= ~clk_n;

end

end

end

assign clk_divider = clk_p | clk_n;

endmodule判断条件需要确认一下,计数器为上升沿触发开始计数,上升沿触发为记完结束,下降沿触发为一半

3.小数分频

/********************************************

计数器实现 3.5 分频,N=3,2N=6

*********************************************/

moduleNpoint5_Divider(

input clk,

input rst_n,

output clk_divider

);

reg[2:0] count_p; //上升沿计数

reg[2:0] count_n; //下降沿计数

regclk_p; //上升沿分频

regclk_n; //下降沿分频

//上升沿计数

always @( posedge clk or negedge rst_n )

begin

if( !rst_n )

count_p <= 3'b0;

else if( count_p == 3'd6 )

count_p <= 3'b0;

else

count_p <= count_p + 1'b1;

end

//上升沿分频

always @ ( posedge clk or negedge rst_n )

begin

if( !rst_n ) begin

clk_p <= 1'b0;

end

else begin

if( count_p == 3'd4 ||count_p == 3'd0 ) begin

clk_p <= ~clk_p;

end

end

end

//下降沿计数

always @( negedge clk or negedge rst_n )

begin

if( !rst_n )

count_n <= 3'b0;

else if( count_n == 3'd6 )

count_n <= 3'b0;

else

count_n <= count_n + 1'b1;

end

//下降沿分频

always @ ( negedge clk or negedge rst_n )

begin

if( !rst_n ) begin

clk_n <= 1'b1;

end

else begin

if( count_n == 3'd4 ||count_n == 3'd1 ) begin

clk_n <= ~clk_n;

end

end

end

assignclk_divider = clk_p & clk_n;

endmodule到了这里,关于FPGA【Verilog分频器】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!