系统上电后,状态机处于 IDLE(初始状态);

接收到有效的单字节数据读/写开始信号i2c_start 后,状态机跳转到 START_1(起始状态);

FPGA 向 EEPROM 存储芯片发送起始信号,随后状态机跳转到 SEND_D_ADDR(发送器件地址状态);

在此状态下向 EEPROM 存 储芯片写入控制指令,控制指令高 7 位为器件地址,最低位为读写控制字,写入“0”,表 示执行写操作;控制指令写入完毕后,状态机跳转到 ACK_1(应答状态)。

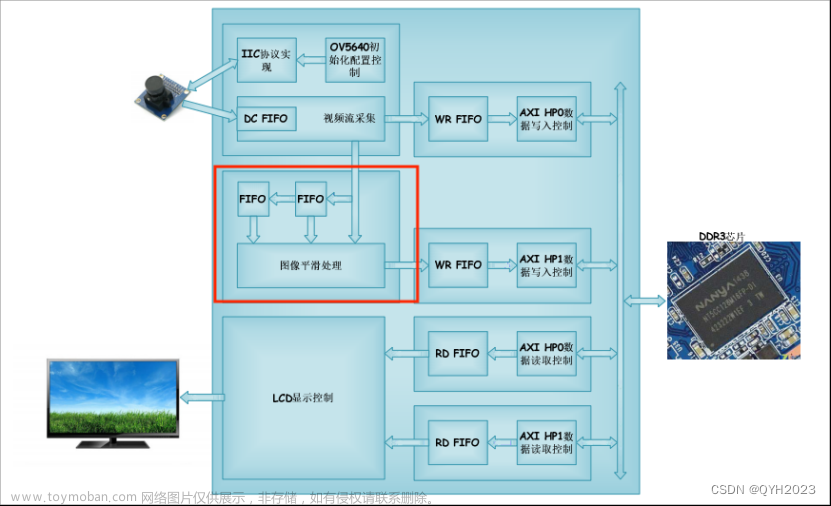

下面讲一下配置寄存器的步骤: ov5640的每个寄存器配置之前都要先写入8位器件地址0X78,然后再写入高低16位寄存器地址,再写入8位数据值

前面第1-2红线之间的state=2在SEND_D_ADDR状态表示要写入器件地址,i2c_sda的0111_1000表示ov5640的器件地址0X78;

第2-3条红线之间的state=3在ACK_1应答状态;

第3-4和第5-6条红线总共表示写入第一个寄存器地址3103;其中第3-4条红线之间的state=4在SEND_B_ADDR_H状态表示要写ACK入寄存器地址高8位,i2c_sda的0011_0001表示0X31;第4-5条红线之间的state=5在ACK_2应答状态;第5-6条红线之间的state=6在SEND_B_ADDR_L状态表示要写入寄存器地址低8位,i2c_sda的0000_0011表示0X03;第6-7条红线之间的state=7在ACK_3应答状态;

第7-8条红线之间的state=8在WR_DATA状态表示要写入第一个寄存器的数据值,i2c_sda的0001_0001表示写入的数据值是0x11;

第8-9条红线之间的state=9在ACK_4应答状态;

在9-10条红线之间的state=f在STOP结束状态;此后i2c_end拉高了一个时钟周期表示一个寄存器配置完成。

每个寄存器配置都是从i2c_start开始,到i2c_end结束的(即两条黄线之间:从state=1~9,再到STOP结束状态f)

本身ov5640的器件地址是0X78(即0111_1000)。但是野火写的器件地址是0X3c(即0011_1100), 但是在i2c_sda_reg的8位SEND_D_ADDR地址中,用cnt_bit计数8个,在前7个写入的是器件地址0X3c(取低位的7个数011_1100),最后一个是读写控制字0(0表示写),合起来也是0X78(即0111_1000)。

文章来源:https://www.toymoban.com/news/detail-828800.html

文章来源:https://www.toymoban.com/news/detail-828800.html

写使能有效,读使能无效(即只是写入了ov5640的寄存器地址和数据值,但不读出),所以只有左边圈住的状态需要操作,右边的没圈住的状态不用管。 文章来源地址https://www.toymoban.com/news/detail-828800.html

文章来源地址https://www.toymoban.com/news/detail-828800.html

到了这里,关于OV5640_top中的i2c_ctrl代码结合仿真波形理解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!