相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

在静态时序分析:SDC约束命令create_clock详解一文的最后,我们谈到了针对理想(ideal)时钟,可以使用set_clock_transition命令直接指定理想时钟到达各触发器时钟引脚的转换时间(这是一种估计),而不是在时钟端口使用set_input_transition命令(即使使用了,对理想时钟也是无效的),因为时钟树尚未创建,时钟端口的高扇出会导致,任何在时钟路径上的转换时间和延迟的计算都是毫无意义的。

该指令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_clock_transition

transition clock_list [-rise] [-fall] [-min] [-max]

//注:该命令的clock_list参数一定要放在transition参数后-rise选项用于指定转换时间应用于时钟的上升沿、-fall选项用于指定转换时间应用于时钟的下降沿。如果这两个选项都没有指定,转换时间同时应用于时钟的上升沿和下降沿(相当于它们同时指定)。

-min选项用于指定转换时间应用于建立时间时序分析、-max用于指定转换时间应用于保持时间时序分析。如果这两个选项都没有指定,转换时间同时应用于建立时间和保持时间分析(相当于它们同时指定)。

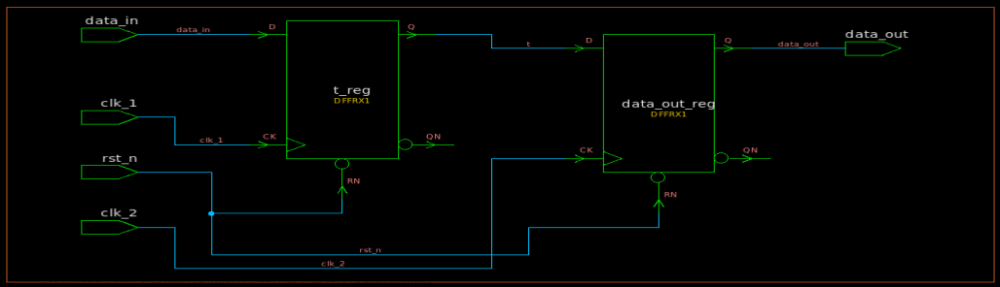

下面举例说明set_clock_transition命令的具体用法,考虑两个触发器组成的简单结构,其中第一个触发器即发射触发器由clk_1时钟控制,第二个触发器即捕获触发器由clk_2时钟控制,有关发射触发器和捕获触发器的内容,可以看以往的文章静态时序分析:建立时间分析-CSDN博客,具体电路结构如图1所示。

图1 简单的例子

现在我们只研究从t_reg的时钟端到data_out_reg的数据输入端的时序路径。首先使用下面的命令在两个时钟端口上分别创建两个理想时钟对象。

create_clock -period 10 -waveform {5 10} [get_port clk_1]

create_clock -period 10 -waveform {5 10} [get_port clk_2] 然后我们使用下面的命令,分别设置这两个理想时钟对象的时钟转换时间,在这里为了区分,设置的数值是不同的,并且转换时间被设置到建立时间和保持时间分析的上升沿和下降沿这四种情况上。

set_clock_transition 0.1 [get_clock clk_1]

set_clock_transition 0.2 [get_clock clk_2]可以使用report_clock -skew命令查看定义了的理想时钟转换时间,如图2所示。

图2 转换时间报告

现在我们使用下面的命令改变clk_1时钟用于保持时间分析的转换时间,结果如图3所示。

set_clock_transition 0.5 -min [get_clock clk_1]

图3 转换时间报告

可以使用reoprt_timing命令报告时序路径的建立时间分析、保持时间分析的时序报告,如图4和图5所示,注意此时要使用-transition_time选项才能显示出时钟端口的转换时间。

图4 建立时间的时序报告

图5 保持时间的时序报告文章来源:https://www.toymoban.com/news/detail-830306.html

注意,set_clock_transition命令只应在预布局阶段(pre-layout)使用,即时钟树综合(CTS)前。一旦时钟树综合完成,使用set_propagated_clock命令将理想时钟变成传播时钟后,时钟上的转换时间属性就会失效,如果需要移除时钟上的转换时间属性,使用remove_clock_transition命令。文章来源地址https://www.toymoban.com/news/detail-830306.html

到了这里,关于静态时序分析:SDC约束命令set_clock_transition详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!