实验题目: 序列检测器设计

实验目的: 掌握应用数字逻辑设计集成开发环境进行序列检测器设计的方法;掌握时序逻辑电路设计的过程。

实验内容:

1、设计一个序列检测器,用于检测输入数据中的特定序列“10010”。

2、实现一个电路,当检测到该序列时,输出为1,否则为0。

3、分析实验结果,验证电路的功能是否符合设计要求。

实验步骤:

1、在数字逻辑集成开发环境中新建一个序列检测器工程;

2、编写Verilog HDL源程序;

3、编译和逻辑综合源程序;

4、编写Verilog HDL仿真测试程序;

5、调用数字逻辑设计仿真环境对源程序进行仿真;

6、安装输入/输出端口建立约束文件;

7、下载到实验开发板,观察实践运行结果。

实验数据记录:

- 写出编写的Verilog HDL源程序。

`timescale 1ns/1ps

module seq_tb();

reg [23:0] d;

reg clk;

reg rst_n;

wire y;

reg data;

seq_test uut (

.clk(clk),

.rst_n(rst_n),

.data(data),

.y(y)

);

initial begin

clk=0;

rst_n=0;

#10;

rst_n=1;

#20;d = 24'b0011_0100_1001_0110_1001_0101;

end

always #10 clk=~clk;

always@(negedge clk) begin

#10 data = d[23];

d = {d[22 : 0], d[23]}; //Parallel to serial

end

endmodule

- 写出编写的Verilog HDL仿真测试程序。

`timescale 1ns/1ps

module seq_test(clk,rst_n,data,y

);

input clk;

input rst_n;

input data;//10010

output y;

reg [2:0] state;

reg [2:0] next_state;

wire y;

parameter s_idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,

s4=3'b100,s5=3'b101,s6=3'b110,s7=3'b111;

always @(posedge clk or negedge rst_n)

begin

if (~rst_n)

next_state <= 0;

else

next_state <= state;

end

always @(posedge clk or negedge rst_n)

begin

if (~rst_n)

state <= s_idle;

else begin

case(state)

s_idle: begin if(data ==1)

state <= s1;

else

state <= s_idle; end

s1: begin if(data ==0)

state <= s2;

else

state <= s1;end

s2: begin if(data ==0)

state <= s3;

else

state <= s7; end

s3: begin if(data ==1)

state <= s4;

else

state <= s6; end

s4: begin if(data ==0)

state <= s5;

else

state <= s1; end

s5: begin if(data == 1)

state <= s1;

else

state <= s3;end

s6: begin if(data == 1)

state <= s7;

else

state <= s6;end

s7: begin if(data == 1)

state <= s1;

else

state <= s2;end

default: state <= s_idle;

endcase

end

end

assign y = (state == s4 && data == 0)?1'd1:1'd0;

endmodule

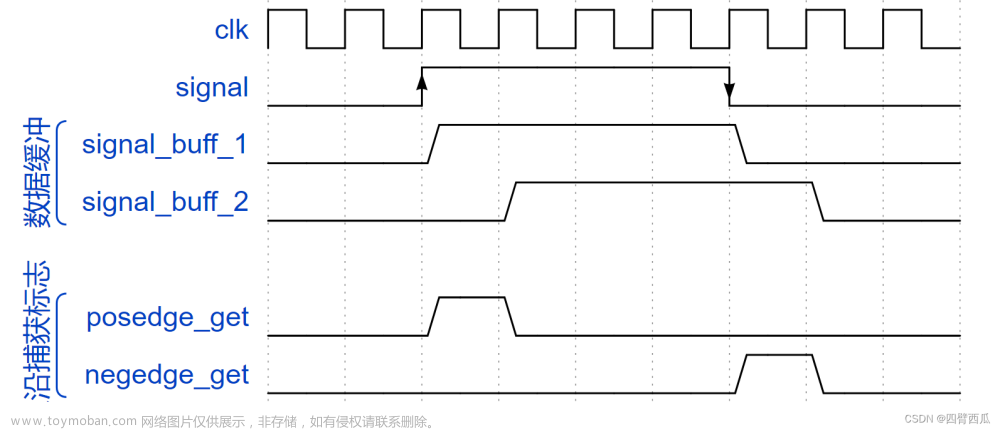

3、画出仿真环境中测试波形图。

问题讨论:文章来源:https://www.toymoban.com/news/detail-831232.html

论述时序逻辑电路中有限状态机设计与实现方法。文章来源地址https://www.toymoban.com/news/detail-831232.html

到了这里,关于【FPGA & Modsim】序列检测的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!