Verilog HDL简介

就是用代码来描述硬件结构

语言有VHDL与Verilog HDL

与VHDL比较

Verilog HDL 是从C语言来的,学的快

Verilog HDL基础语法

逻辑值

###例子

关键字

也叫保留字,一般是小写

module

表示模块的开始

endmodule

模块的结束

模块名

一般与.v文件的名字一致

输入信号

input

输出信号

output

既做输入也做输出

inout

需要一些变量和参数对输入信号进行处理得到输出信号,变量又分为两种类型

线网型变量 wire

可以看作直接的链接,可以映射为一条真实存在的物理连线

寄存器型变量 reg

对某一时间点状态进行保持的功能,可以映射为一条真实的元器

参数 parameter

实例化可以修改参数

参数 localparam

只能在模块内部使用,不能实例化

常量

基数表示法

格式:[ 换算为二进制后位宽的总长度 ] [ ’ ] [ 数值制符号 ] [ 与数值进制符号对应的数值 ]

8‘d171:位宽是8bit,十进制的171。

[数值进制符号]中如果是[h]则表示十六进制,如果是[o]则表示八进制,如果是[b]则表示二进制,D 表示十进制

8’hab表示8bit的十六进制数ab,

8’o253表示8bit的八进制数253:

8’b10101011表示8b性的二进制数10101011,下划线增强可读性。

[换算为过进制后位宽的总长度]:可有可无,verilog会为常量自动匹配合适的位宽。

当总位宽大于实际位宽,则自动在左边补0,总位宽小于实际位宽,则自动截断左边超出的位数。

'd7与8’d7:表示相同数值,8’d7换算为二进制就是8’b0000—0111,前面5位补0;

2’d7换算为二进制就是2’b11,超过2位宽的部分被截断。

如果直接写参数,例如100,表示位宽为32bit的十进制数100·

赋值方式

赋值方式有两种,一种是阻塞赋值,一种是非阻塞赋值

阻塞赋值

可以理解为顺序执行,即第一句语句执行玩之后才会执行第二句语句

非阻塞赋值

语句是并行执行,同一时刻两条语句同时执行

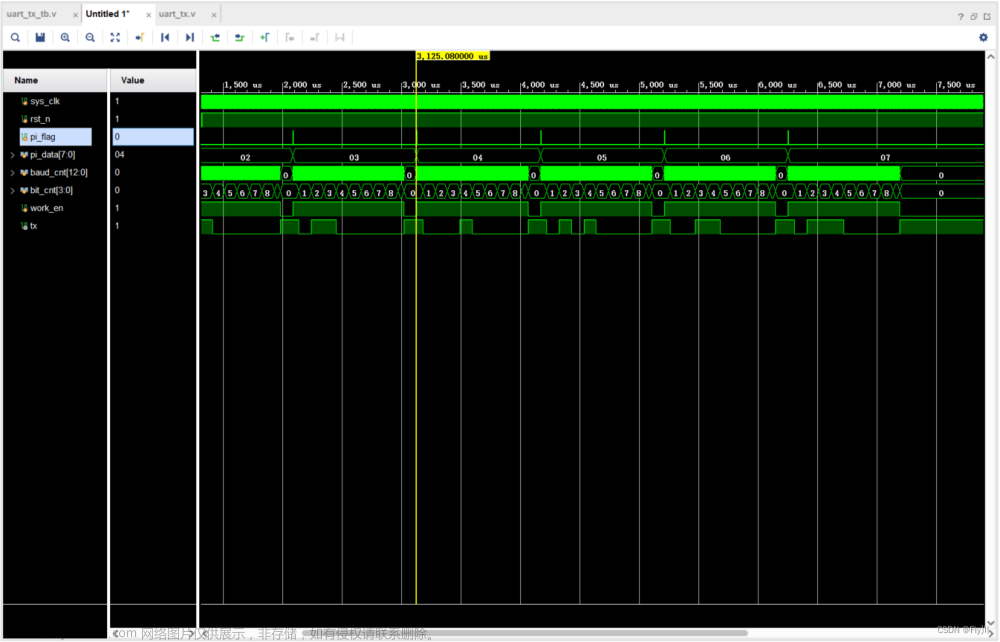

always语句

使用前面定义的计数器

当复位信号有效时,我们给变量cnt初值是0.如果计数到最大值我们设定的参数时,就一直保持最大值,如果没有技术到最大值,每个时钟周期值+1

assign 语句

如果括号内的条件满足的话,就将第一个值赋值给某一个变量,如果不满足的话,就将第二个值赋值给这个变量

算数运算符

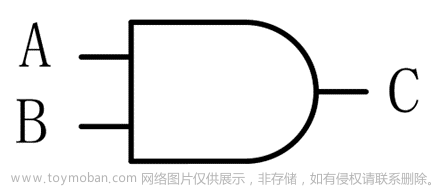

归元运算符、按位运算符

逻辑运算符

关系运算符

移位运算符

位拼接运算符

条件运算符

优先级

if-else 条件分支语句

case分支控制语句

系统函数

display

write

strobe

但是只在最后执行

monitor

stop ,finish

继续仿真不是从头开始执行的,而是从暂停的地方开始执行的

time,random

文章来源:https://www.toymoban.com/news/detail-833023.html

文章来源:https://www.toymoban.com/news/detail-833023.html

readmemb,readmemh

文章来源地址https://www.toymoban.com/news/detail-833023.html

文章来源地址https://www.toymoban.com/news/detail-833023.html

到了这里,关于【FPGA Verilog开发实战指南】初识Verilog HDL-基础语法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!