简介

对于高速IO口配置光纤,现在目前大部分开发板都有配置,且也有说明,在此根据自己的工作经验以及对于各开发板的说明归纳

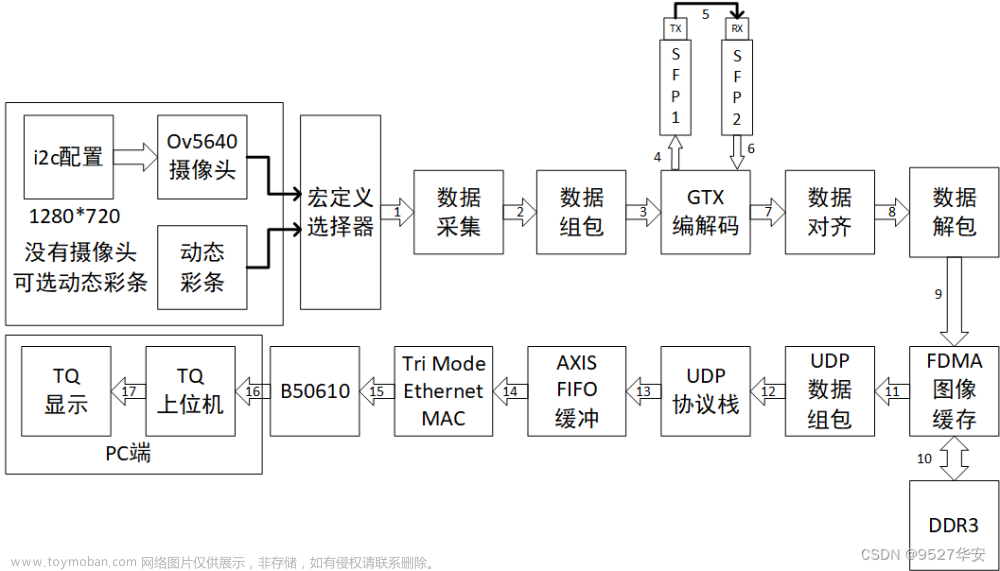

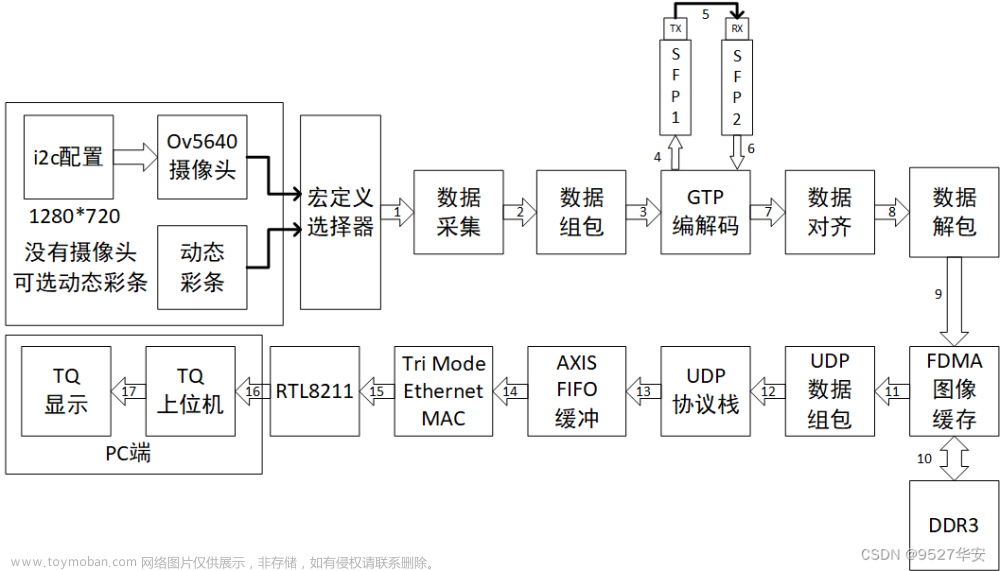

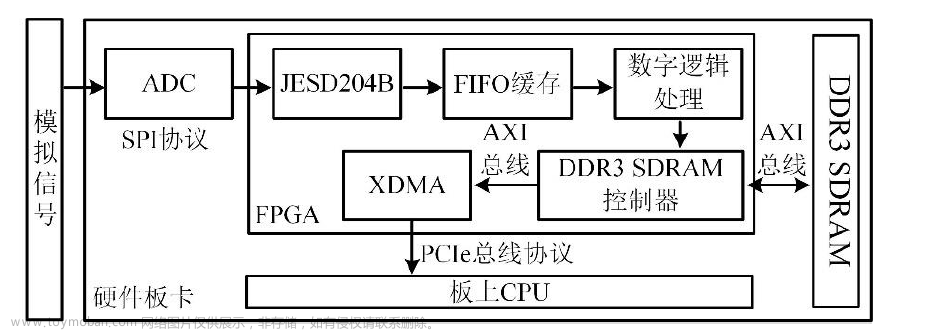

通过高速IO接口,以及硬件配置,可以实现对于光纤的收发功能,由于GTX的速率在500Mbs到10Gbps之间,但通道高速io可配置光纤10G硬件,物理通完成,则可传输常见的光纤协议,例如UDP协议,FC-AC协议,ARINC818协议等来完成对于视频的发送和接收功能。

原理框图

如上图所示,高速IO接口,以及时钟基准输入,能够完成对于光纤的收发功能

原理图

软件配置

软件配置,参考1.25G光纤协议,使用8B/10B编码,以及K28.5掩码来完成配置,最后通过官方自带的例程作为验证即可。值得注意的是,时钟、数据、收发都是位置都是固定的不可随意切换,否则编译过不了。文章来源:https://www.toymoban.com/news/detail-833961.html

文章来源地址https://www.toymoban.com/news/detail-833961.html

文章来源地址https://www.toymoban.com/news/detail-833961.html

到了这里,关于基于FPGA的视频接口之高速IO(光纤)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!