qspi_50m.xdc文件:文章来源:https://www.toymoban.com/news/detail-834951.html

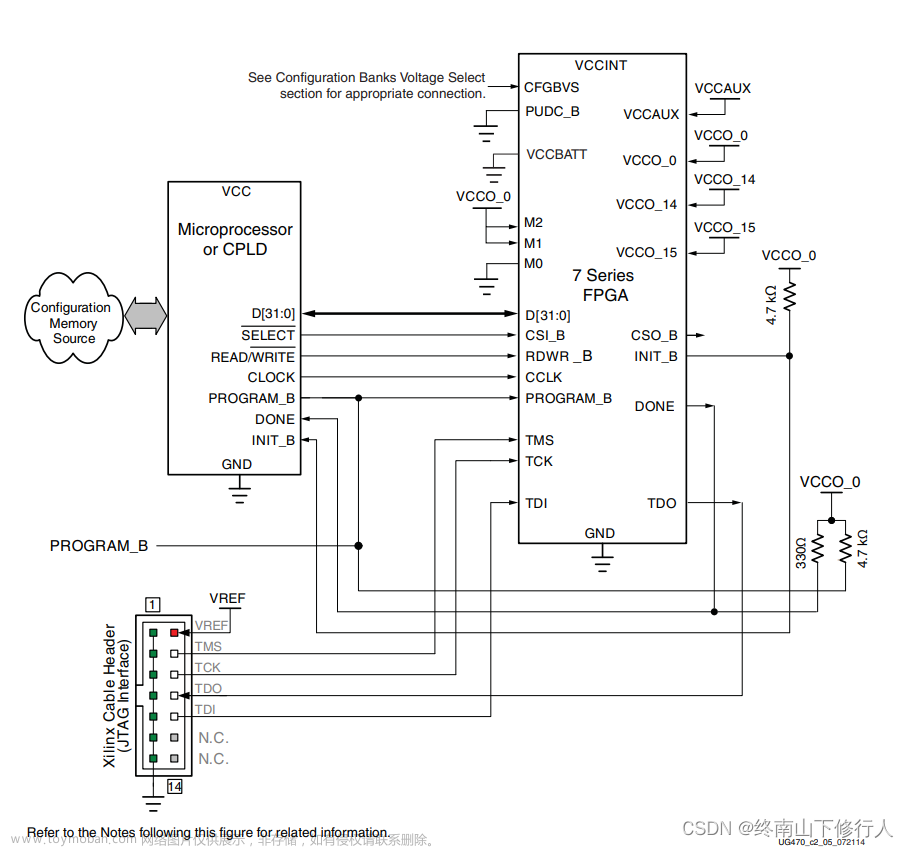

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

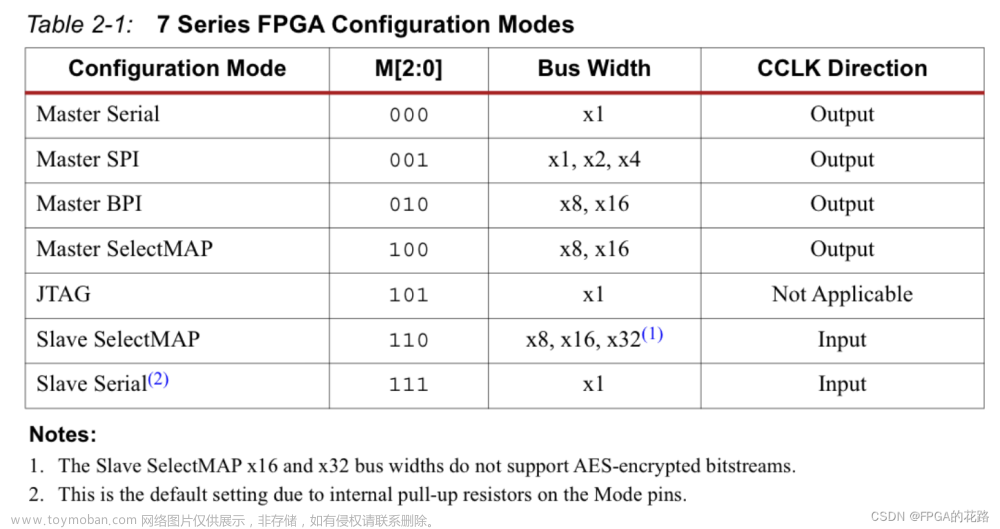

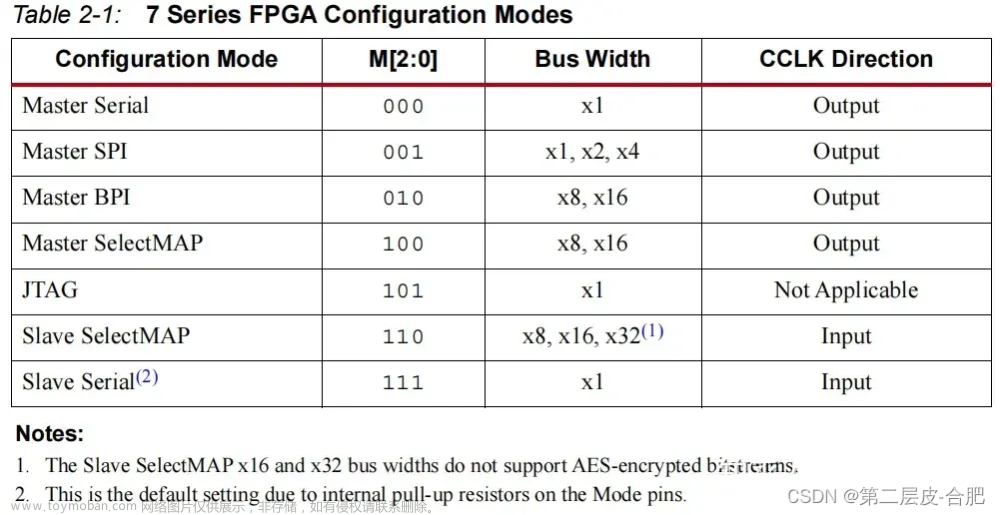

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

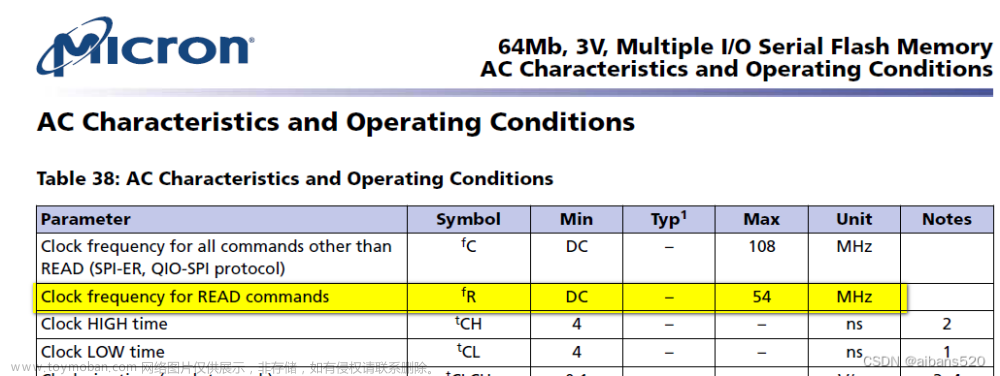

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

等同于图形化配置方式:

文章来源地址https://www.toymoban.com/news/detail-834951.html

文章来源地址https://www.toymoban.com/news/detail-834951.html

到了这里,关于Xilinx FPGA SPIx4 配置速度50M约束语句(Vivado开发环境)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!