目录

1.算法仿真效果

2.算法涉及理论知识概要

2.1 卷积码编码

2.2 RS码编码

2.3 级联编码

2.4 解码过程

3.Verilog核心程序

4.完整算法代码文件获得

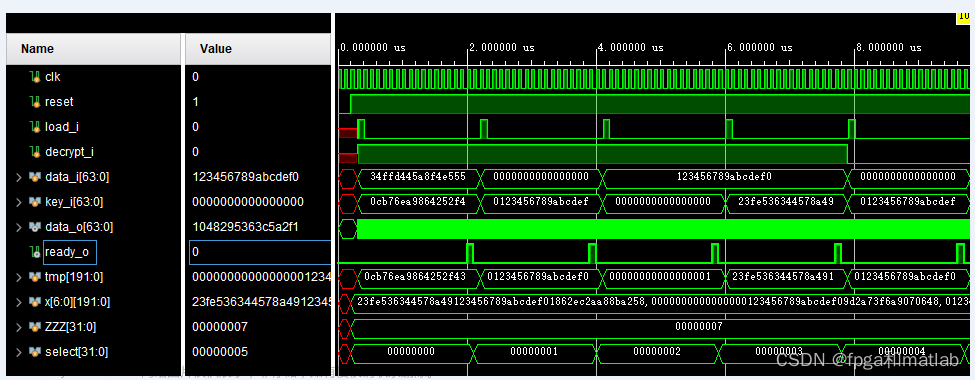

1.算法仿真效果

Vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

级联码是一种通过将两种或多种纠错码结合使用来提高纠错能力的编码方案。在RS+卷积级联编码中,通常首先使用卷积码对原始数据进行编码,以增加冗余并提供一定的纠错能力。然后,将卷积码的输出作为RS码的输入进行进一步编码,以增加更强的纠错能力。

2.1 卷积码编码

卷积码是一种通过引入冗余来提高数据传输可靠性的纠错码。在编码过程中,原始数据被分成多个小块,并与生成多项式进行卷积运算以产生冗余校验位。

卷积码通常使用(n, k, m)来表示,其中n表示输出码字的位数,k表示输入数据的位数,m表示编码器的记忆长度。卷积码的生成函数可以用多项式来表示,例如G(D) = [1 + D + D^2, 1 + D^2](这是一个(2, 1, 2)卷积码的示例)。

编码过程可以表示为:

C(D) = U(D) * G(D)

其中,U(D)是原始数据的多项式表示,G(D)是生成多项式的矩阵表示,C(D)是编码后的输出多项式。

2.2 RS码编码

RS码是一种非二进制线性块码,它通过在有限域上进行多项式运算来提供强大的纠错能力。RS码通常表示为RS(n, k),其中n表示码字的长度,k表示信息符号的数量。

在RS编码过程中,原始数据被视为有限域上的多项式系数,并通过选择一个适当的生成多项式来生成冗余校验符号。生成多项式通常是一个固定次数的多项式,其根是有限域中的某些元素。

编码过程可以表示为:

C(x) = M(x) * G(x) mod (x^n - 1)

其中,M(x)是原始数据的多项式表示,G(x)是生成多项式,C(x)是编码后的输出多项式。

2.3 级联编码

在RS+卷积级联编码中,首先将原始数据通过卷积码编码器进行编码,生成具有一定纠错能力的卷积码输出。然后,将卷积码的输出作为RS码编码器的输入,进一步进行RS编码,以增加更强的纠错能力。

级联编码的好处是可以结合两种码的优点,卷积码可以提供连续的错误纠正能力,而RS码可以提供强大的突发错误纠正能力。

2.4 解码过程

解码过程是编码过程的逆过程。首先,对接收到的信号进行RS解码,纠正其中的突发错误。然后,将RS解码的输出作为卷积码解码器的输入,进行卷积解码,纠正其中的连续错误。解码过程通常使用最大似然解码算法,如Viterbi算法,来找到最可能的发送序列。

RS+卷积级联编译码通过结合卷积码和RS码的优点,提供了一种高效的纠错方案。卷积码提供连续的错误纠正能力,而RS码提供强大的突发错误纠正能力。通过级联编码和解码过程,可以实现更高的数据传输可靠性和错误纠正能力。

3.Verilog核心程序

RTL结构图

文章来源:https://www.toymoban.com/news/detail-835033.html

文章来源:https://www.toymoban.com/news/detail-835033.html

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/29 22:08:05

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST;

reg i_clk;

reg i_clks;

reg i_rst;

wire [7:0]i_din;

wire i_enable;

//编码

wire [7:0]o_RS_enc_dat;

wire o_RS_enc_enable;

wire [1:0]o_conv_enc_dat;

wire o_conv_dec_dat;

wire o_conv_dec_enable;

wire [7:0]o_enc_dat_err;

wire o_enc_enable_err;

//译码

wire [7:0]o_RS_dec_dat;

wire o_RS_dec_enable;

reg[11:0]frames;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

frames <= 11'd0;

end

else begin

frames <= frames+12'd1;

end

end

assign i_din = (frames>=12'd2 & frames<=12'd211)?frames-1:8'd0;

assign i_enable = (frames>=12'd2 & frames<=12'd211)?1'b1:1'd0;

wire [7:0]o_enc_dat_err;

wire o_enc_enable_err;

tops topsu(

.i_clk (i_clk),

.i_clks (i_clks),

.i_rst (i_rst),

.i_din (i_din),

.i_enable (i_enable),

.o_RS_enc_dat (o_RS_enc_dat),//编码out

.o_RS_enc_enable(o_RS_enc_enable),

.o_conv_enc_dat (o_conv_enc_dat),//212卷积编译码

.o_conv_dec_dat (o_conv_dec_dat),

.o_conv_dec_enable(o_conv_dec_enable),

.o_enc_dat_err (o_enc_dat_err),//编码out+误码

.o_enc_enable_err (o_enc_enable_err),

.o_RS_dec_dat (o_RS_dec_dat),//译码out

.o_RS_dec_enable (o_RS_dec_enable)

);

initial

begin

i_clk=1'b1;

i_clks=1'b1;

i_rst=1'b1;

#1000

i_rst=1'b0;

end

always #80 i_clk=~i_clk;

always #10 i_clks=~i_clks;

endmodule

00_057m4.完整算法代码文件获得

V文章来源地址https://www.toymoban.com/news/detail-835033.html

到了这里,关于m基于FPGA的RS+卷积级联编译码实现,RS用IP核实现,卷积用verilog实现,包含testbench测试文件的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!