名称:基于FPGA的音乐喷泉控制Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

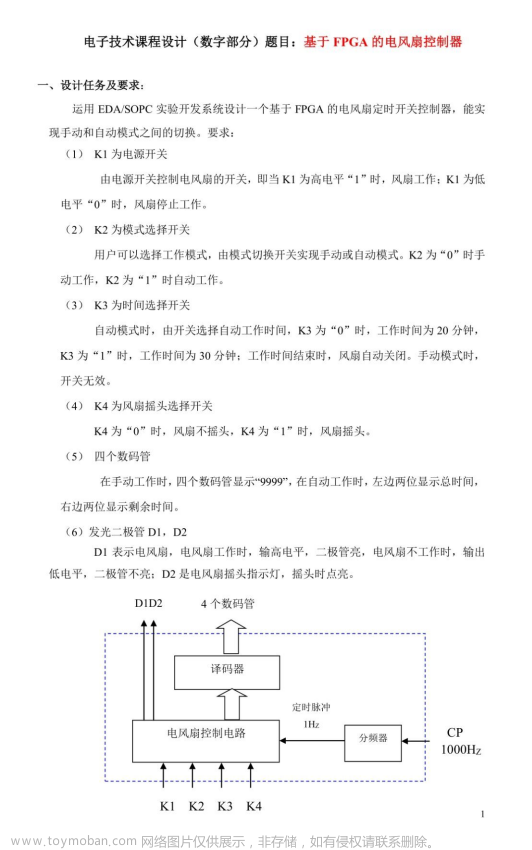

代码功能:

基于FPGA的音乐喷泉控制

1、具有启动控制按键,按下后开始

2、喷泉具有6个喷嘴,可以手动切换三种工作模式

3、输入的音乐信号分为低音、中音、高音

4、将输入的音转换为对应的pwm波占空比参数

5、不同的工作模式下,6个喷嘴对应pwm波的分部不同

音乐喷泉

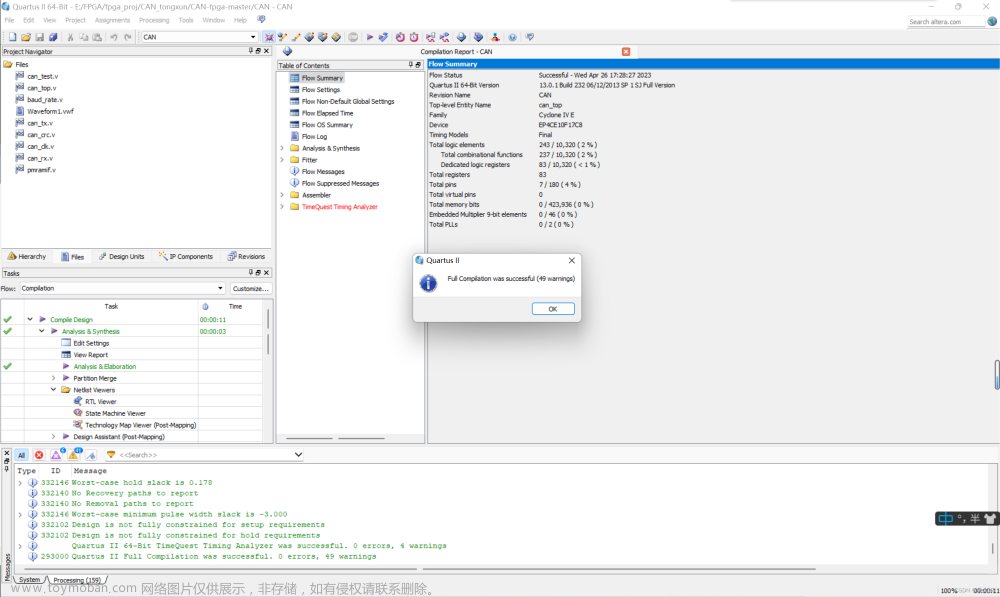

1.程序文件

2.程序运行

3.程序RTL图

4.Testbench

5.仿真图

fountain_out为输出的6喷嘴[5:0],喷嘴输出为不同占空比的PWM波

Mode 切换不同模式

Start为高电平时启动

高中低对应的占空比不一样

输出的6个喷嘴,下图中喷嘴5,3,1分别对应高、中、低,4,2,0未打开,不同模式下对应喷嘴不同,启动的喷嘴也不同。

下图中可看到不同模式下喷嘴启动不一样。

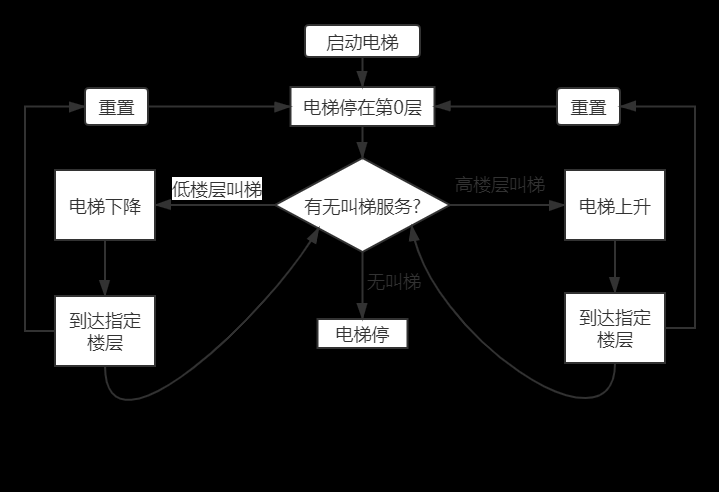

状态机

状态图

部分代码展示:文章来源:https://www.toymoban.com/news/detail-836864.html

module Musical_fountain( input clk, input start,//为高电平时开启 input [1:0] mode,//三种模式,00,01,10 input [2:0] low_music,//低音,0~7 input [2:0] mid_music,//中音,0~7 input [2:0] hig_music,//高音,0~7 output [5:0] fountain_out //6个喷嘴输出 ); wire [7:0] low_music_zkb; wire [7:0] mid_music_zkb; wire [7:0] hig_music_zkb; //将输入的音转换为对应的pwm占空比参数 zhankongbi low_music_zhankongbi( . clk(clk), . voice(low_music), . pwm_zhankongbi(low_music_zkb) ); //将输入的音转换为对应的pwm占空比参数 zhankongbi mid_music_zhankongbi( . clk(clk), . voice(mid_music), . pwm_zhankongbi(mid_music_zkb) ); //将输入的音转换为对应的pwm占空比参数 zhankongbi hig_music_zhankongbi( . clk(clk), . voice(hig_music), . pwm_zhankongbi(hig_music_zkb) ); //分频100 reg [7:0] pwm_cnt=8'd0; always@(posedge clk) if(pwm_cnt>=8'd100) pwm_cnt<=8'd0; else pwm_cnt<=pwm_cnt+8'd1; reg low_music_pwm=0; reg mid_music_pwm=0; reg hig_music_pwm=0; always@(posedge clk) if(start==0) low_music_pwm<=0; else if(low_music_zkb>pwm_cnt) low_music_pwm<=1;//产生低音PWM波 else low_music_pwm<=0; always@(posedge clk) if(start==0) mid_music_pwm<=0; else if(mid_music_zkb>pwm_cnt) mid_music_pwm<=1;//产生中音PWM波 else mid_music_pwm<=0; always@(posedge clk) if(start==0) hig_music_pwm<=0; else if(hig_music_zkb>pwm_cnt) hig_music_pwm<=1;//产生高音PWM波 else hig_music_pwm<=0; reg [5:0] fountain=6'd0; parameter S0=2'b00; parameter S1=2'b01; parameter S2=2'b10; reg [1:0] state=2'b00; always@(posedge clk) case(state)//mode控制不同模式,即改变喷嘴对应不同的音,可自己组合 S0: if(mode==2'b01) state<=S1; else if(mode==2'b10) state<=S2; else state<=S0; S1: if(mode==2'b00) state<=S0; else if(mode==2'b10) state<=S2; else state<=S1; S2: if(mode==2'b00) state<=S0; else if(mode==2'b01) state<=S1; else

源代码

扫描文章末尾的公众号二维码文章来源地址https://www.toymoban.com/news/detail-836864.html

到了这里,关于基于FPGA的音乐喷泉控制Verilog代码Quartus仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!