本文以TC3系列MCU为例,先来了解中断源是如何产生的,再看一下CPU是如何处理中断源的。

AURIX TC3XX的中断路由模块 Interrupt Router (IR)

在TC3中,中断既可以被CPU处理,也可以被DMA处理,所以手册中不再把中断称为中断,而是称为服务,我们为了方便还是叫中断,但在后文的英文名称或简写中经常出现Service,大家当中断来理解就好。

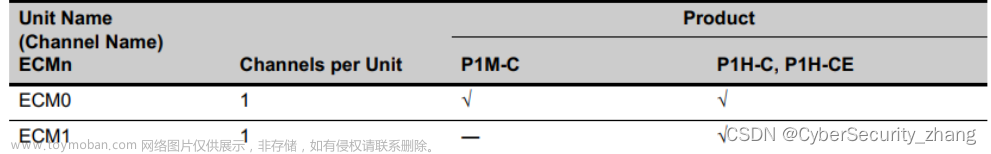

IR模块支持1024个中断请求节点(SRN),每个节点就可以理解成一个触发中断的源,比如CAN外设、外部IO中断、软件触发的中断等。每个SRN都有一个单独的中断请求控制寄存器SRC,寄存器的定义如下文所示,这里重点关注四个:

- TOS:中断处理类型,是由CPU处理还是由DMA处理,多核单片机还决定由哪个核来处理;

- SRPN:中断请求优先级编号,如果该中断由CPU处理,那么这个编号将会被传递给CPU,CPU用来判断中断与当前任务的优先级孰高孰低,具体处理方式见下文。如果该中断由DMA来处理,那么这个编号表示该中断由哪个DMA通道进行处理,所以值不能大于可用的DMA通道的数量。

- SRR & SRE:SRR是中断请求标志,当中断发生时置位,但只有当SRE=1时,中断请求才会被发送给CPU,此时CPU处理完中断请求后(注意处理完中断请求不是执行完中断处理函数,而是决定了是否接受该中断)硬件会自动清除SRR,不建议软件清除SRR。如果SRE=0,中断请求不会被发送给CPU,此时CPU可以通过轮询的方式查询SRR,看中断是否发生,如果发生了则进行处理,注意这种情况下要软件手动清除SRR。

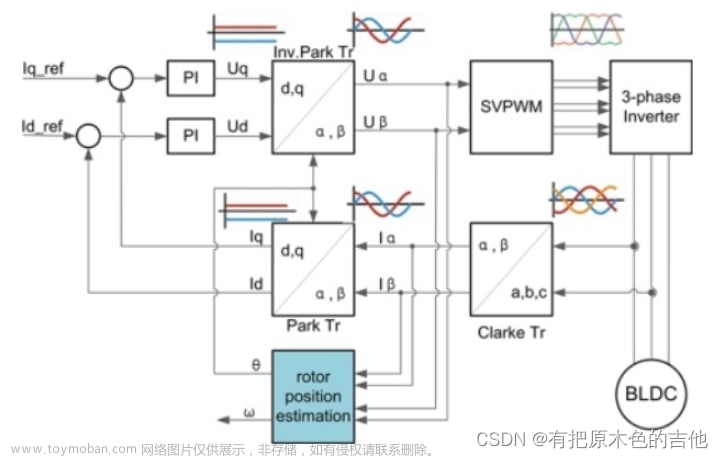

整个IR模块的架构图如下图所示:

SRPN的长度是8位,范围是0-255,但如果中断是由CPU来处理的,那么SRPN=0是没有意义的,也就是最小的有效优先级是1。对于TOS相同的中断源,SRPN最好都是唯一的,同一个中断组(中断组的定义见下文)内的SRPN可以相同,但当相同优先级的中断发生时,执行顺序不能确定。

IR模块中有7个中断控制单元ICU,分别对应6个核和DMA,对于TOS相同的中断,如果同时触发,ICU会先根据优先级进行一次仲裁,将优先级更高的传递给CPU或DMA。对于需要CPU处理的中断源,请求发送给CPU之后会形成一个待处理的中断优先级编号(PIPN),CPU把PIPN与当前的CPU优先级(CCPN)进行比较,如果CPU接受这个中断请求,则会进行处理,并将该中断请求优先级编号返回给ICU,ICU会清除该中断源的SRR位。

软件中断

任何一个中断请求节点都可以使用软件触发,直接操作SRC寄存器向SETR写入1即可,但中断源触发后没办法区分这次是由软件触发的还是由硬件触发的,所以建议软件中断和硬件中断分别使用不同的中断请求节点。此外还设置了8个GPSR,这8个中断请求节点只能由软件触发,没有关联硬件触发源,所以软件中断建议使用这8个中断请求节点。

下文我们着重看一下CPU如何处理一个中断请求,以下内容来自于Tricore内核手册。

寄存器ICU Interrupt Control Register (ICR)

内核中有一个中断控制寄存器ICR,定义如下,从PIPN的定义可以看出,Tricore的中断优先级数值越大,优先级越高。

CPU处理中断请求

CPU先检查ICR中的IE位,只有当IE = 1时CPU才能处理中断。如果IE = 1,CPU检查PIPN,如果PIPN > CCPN,CPU可以进入中断处理函数。PIPN用来决定中断处理函数在中断向量表中的位置。

以下情况会阻塞中断的处理:

① IE = 0

② CCPN ≥ PIPN

③ CPU正在进入中断或Trap

④ CPU正在执行不可打断的Trap

⑤ CPU正在执行multi-cycle instruction

⑥ CPU正在执行修改ICR寄存器的指令

总结可知,Tricore支持更高优先级的中断打断当前正在执行的中断,但如果新的中断优先级更低,CPU是直接丢弃还是在当前中断处理完成后再进行处理,没有找到具体的依据,但手册中是这样说的:以上原因会block the CPU from immediately responding to the interrupt request generated by the ICU,也就是说不能立即处理,感觉应该是条件满足的时候还是会处理。

CPU进入中断处理函数

CPU处理完中断请求,并确定要执行中断处理函数后,会执行以下操作

- 保存上下文环境

- ICR.IE = 0. 之前的 ICR.IE 会被保存到 PCXI.PIE

- ICR.CCPN 被保存到 PCXI.PCPN

- ICR.PIPN 被保存到 ICR.CCPN

- 查找中断向量表,执行ISR的第一条指令

值得注意的是,进入中断处理函数后全局中断IE会被关闭,用户可以自行决定在中断中是否打开全局中断。

CPU退出中断处理函数

- 上面保存的ICR.IE、ICR.CCPN、ICR.PIPN等上下文环境被恢复。

中断向量表

中断向量表存储在ROM中,是一个包含ISR入口函数地址的有序数组。当CPU收到一个中断请求的时候,CPU根据ICR.PIPN计算出一个偏移地址,再加上BIV寄存器中存储的中断向量表起始地址,得到实际中断入口函数的地址,将这个地址装入PC指针中。

BIV寄存器必须要在全局中断使能前设置好,且同一套程序中可以通过修改BIV寄存器使能不同的中断向量表。

中断向量表中每个中断所占用的地址空间大小可以设置为32字节或8字节,通过BIV寄存器中的VSS进行设置。BIV寄存器的定义如下:

中断入口函数起始地址的计算方式如下:

当VSS = 0的时候:ISR_Entry_PC = BIV | (PIPN<<5);

当VSS = 1的时候:ISR_Entry_PC = BIV | (PIPN<<3);

软件管理中断

上面自动查找中断向量表的方式可以理解为硬件管理中断,此外Tricore提供了一种软件管理中断的机制,即所有的中断入口函数都是同一个,进入这个函数后,再用软件分辨中断的优先级,跳转到相应的中断处理函数。这种方法会降低中断的处理效率,但可以增加中断向量表的灵活性。实现方法如下:

BIV的值设置为0xXXXXYFE0,其中X可以是有效地址范围内的任意数值,但Y必须是 1/3/5 ……单数。BIV设置为这样的值后,所有的中断就都会进到BIV所指向的地址处的函数,所以第一级中断处理函数必须放到BIV所指向的地址。一级中断处理函数中判断优先级,再跳到不同的二级中断处理函数,例子如下,其中 IfxCpu_Irq_swIntVector 可以是软件自定义的中断向量表。

IFX_INTERRUPT_INTERNAL(IfxCpu_Irq_intVecTable, 0, 255)

{

Ifx_CPU_ICR icr;

icr.U = __mfcr(CPU_ICR); /*Fetch the ICR value */

/*Call the ISR */

IfxCpu_Irq_swIntVector[icr.B.CCPN]();

}

中断优先级组

Tricore允许将几个中断划为一组,同一组内的中断不能相互打断。具体实现方式如下:文章来源:https://www.toymoban.com/news/detail-837048.html

上文我们说到,CPU处理中断的时候,会将ICR.PIPN 被保存到 ICR.CCPN,此时如果再来一个中断,就会将新的PIPN 与 CCPN(即旧的PIPN)进行比较,如果优先级更高则当前中断被打断,去处理新的中断。如果某几个中断被设置为一组,那么CPU处理中断的时候,会将该组内最高优先级的PIPN保存到ICR.CCPN,也就是说如果当前组内的其他中断再被触发了,那么新触发的PIPN也不会大于CCPN,所以当前组内的更高优先级的中断也不能打断当前正在执行的中断了。只有当新的中断的优先级大于组内最高优先级的时候,中断才会被打断。文章来源地址https://www.toymoban.com/news/detail-837048.html

到了这里,关于英飞凌 Tricore 架构中断系统详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!