计算机组成原理之机器:存储器之高速缓冲存储器

笔记来源:哈尔滨工业大学计算机组成原理(哈工大刘宏伟)

Chapter3:存储器之高速缓冲存储器

3.1 概述

3.1.1 为什么用cache?

角度一:I/O设备向主存请求的级别高于CPU访存,这就出现了CPU等待I/O设备访存的现象,致使CPU空等一段时间,降低CPU工作效率。为避免CPU与I/O设备争抢访存,可在CPU与主存之间加一级缓存,这样主存可将CPU要取的信息提前送至缓存,一旦主存在与I/O设备交换时,CPU可直接从缓存中读取所需信息,不必空等而影响效率。—引自《计算机组成原理》唐朔飞

角度二:主存速度提高始终跟不上CPU的发展。希望由高速缓存cache来解决主存与CPU速度不匹配的问题—引自《计算机组成原理》唐朔飞

局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。

时间局部性:程序中的某条指令一旦执行,不久后该指令可能再次执行

空间局部性:一旦程序访问了某个存储单元,不久后其附近的存储单元也将被访问

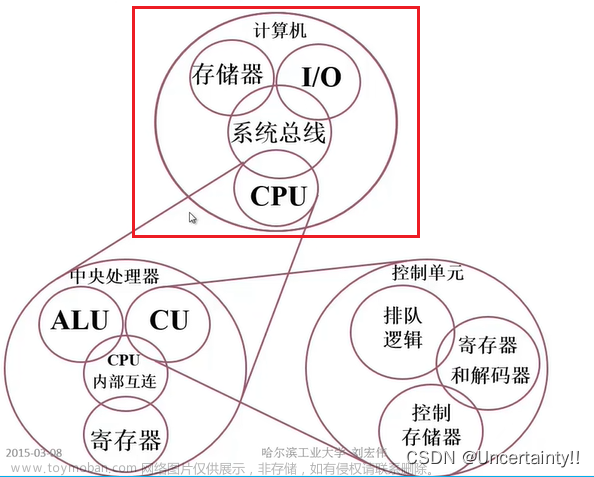

3.1.2 cache的工作原理

主存和缓存的编址

为了与cache映射,将主存与缓存都分成若干块,每块内又包含若干个字,并使它们的块大小相同(即块内的字数相同)

命中与未命中

任何时刻都有一些主存块处在缓存块中。

CPU欲读取主存某字时,有两种可能:

命中:一种是所需要的字已在缓存中,即可直接访问Cache(CPU与Cache之间通常一次传送一个字);

未命中:另一种是所需的字不在Cache内,此时需将该字所在的主存整个字块一次调入Cache中(Cache与

主存之间是字块传送)。如果主存块已调入缓存块,则称该主存块与缓存块建立了对应关系。

—引自《计算机组成原理》唐朔飞

cache的命中率

我们都希望CPU对主存的访问尽可能都转化为对缓存的访问,也就是说我们希望命中率越高越好

cache-主存系统的效率

3.1.3 cache的基本结构

cache和主存之间是以块为单位进行数据传送的,cache和主存的块内地址一致,再看块号,根据映射规则,检查是否命中(CPU所访问的数据在cache中是否存在),如果命中,则形成cache的块号。如果未命中,则检查当前cache是否仍可装入块,若可装入,则将要访问的块装入cache,若没有空间装入,则将某一块与要访问的块进行替换,也就是将要访问的块从内存中调入,把cache中暂时不访问的块换下

主存与cache映射就是主存中的块应该放在cache的哪个位置

主存与cache变换就是主存的地址转换为cache的地址,在cache中找到相对应的主存块

主存与cache之间有直接通路,它完成了两者之间的信息交换

3.1.4 cache的读写操作

写操作可能会造成主存和cache数据的不一致,例如只对主存写而没有对cache写

3.1.5 cache的改进

(1)增加cache级数

CPU内部装cache、CPU外部装cache

(2)统一缓存和分立缓存

统一缓存:把指令和数据统一放在一个cache中

分立缓存:将指令和数据分别放在不同cache中

3.2 cache-主存的地址映射

3.2.1 直接映射(固定的映射关系)

主存当中任意一个给定的块只能装载到某一个指定的cache的块当中

每个区的第0块放到cache中字块0中,每个区的第1块放到cache中字块1中以此类推

主存地址分为两部分:低c位指cache的字块地址、高t位指主存字块标记,它被记录在建立了对应关系的缓存的“标记”位中。

当缓存接到CPU送来的主存地址后,只需根据中间c位字段找到cache字块(如c位字段为00……01找到cache字块1),然后根据字块的“标记”是否与主存地址的高t位相符来判断。

每个缓存块可以和若干个主存块对应

每个主存块只能和一个缓存块对应

3.2.2 全相联映射(灵活性大的映射关系)

主存的任何一个字块可放到任何一个cache字块中

3.2.3 组相联映射(上述两种映射的折中)

主存中每个区的第0块可以放到cache中第0组两个字块的任意一个 文章来源:https://www.toymoban.com/news/detail-838090.html

文章来源:https://www.toymoban.com/news/detail-838090.html

3.3 替换算法

当cache中已满且CPU要访问的数据不在其中,这时就需要将cache中某个块与主存中CPU要访问的块进行替换

先进先出(FIFO)算法

最先被放入cache中的块被替换

近期最少使用(LRU)算法

在cache中选择最⻓时间没有被CPU访问的块进行置

换,也就是说,该算法假设已经很久没有使用的块很有可能在未来较长的⼀段时间内仍然不会被使⽤文章来源地址https://www.toymoban.com/news/detail-838090.html

到了这里,关于计算机组成原理之机器:存储器之高速缓冲存储器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!