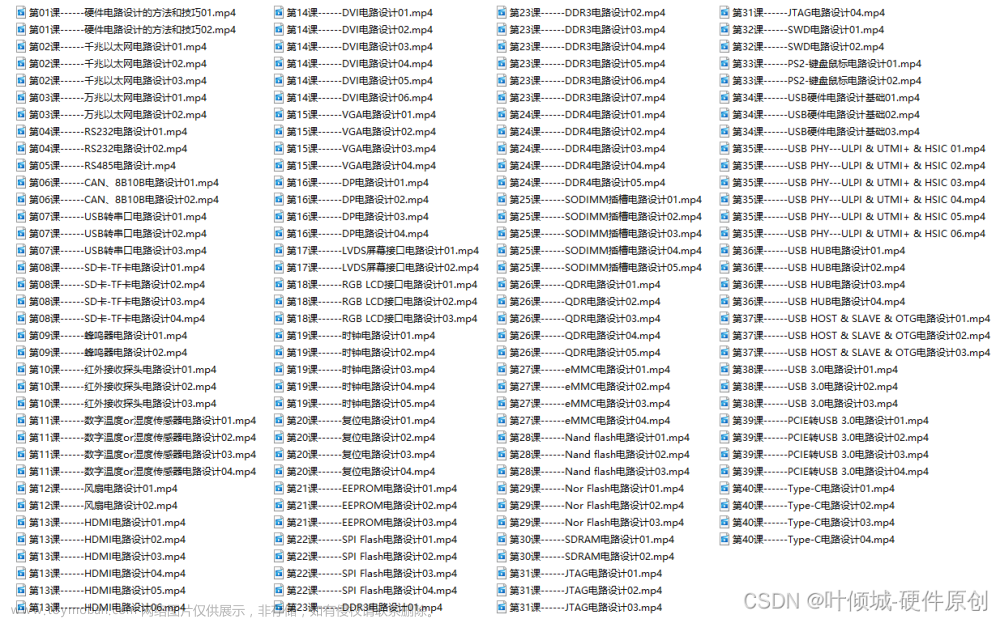

视频链接

ZYNQ7100板级系统硬件实战01_哔哩哔哩_bilibili

FPGA- ZYNQ7100板级原理图硬件实战

1、基于XC7Z100-2FFG900的FPGA硬件实战框图

板卡主要由ZYNQ7100主芯片,6片DDR3,1片eMMC,2个QSPI FLASH和一些外设接口组成。ZYNQ7100 采用Xilinx公司的Zynq7000系列的芯片,Xilinx ARM + FPGA芯片型号为XC7Z100-2FFG900。ZYNQ710 芯片可分成处理器系统部分Processor System(PS)和可编程逻辑部分Programmable Logic(PL)。

在ZYNQ7100芯片的PS端挂了2片DDR3, PL端挂了4片DDR3,每片DDR3容量高达512M字节,使得ARM系统和FPGA系统能独立处理和存储的数据的功能。PS端的8GB eMMC FLASH 存储芯片和2片256Mb的QSPI FLASH 用来静态存储ZYNQ的操作系统、文件系统及用户数据。

丰富的外围接口,其中包含1个PCIex8 接口、1路千兆以太网接口、1路USB 2.0 OTG接口、1路UART串口接口、1路SD卡接口、1个FMC HPC扩展接口,2路SMA接口,和一些按键LED。

适用于高速数据传输交换、数据处理存储、视频传输处理、 以太网通信、以及工业控制等。

1.1功能和接口

1.2、时钟框图

板卡上分别为PS系统和PL逻辑部分提供了单端有源时钟,使PS系统和PL逻辑可以单独工作。另外板上有一个可编程的时钟芯片SI5338P为高速收发器GTX提供差分时钟源。

一般使用的zynq的PL端时钟为50MHz;ps时钟为33.33MHz;

1.3、复位框图

1.4、电源框图(S7课详解)

2、模块化电路设计

2.1、ZYNQ电路

2.2、时钟电路(参考19课)

板卡上分别为PS系统和PL逻辑部分提供了单端有源时钟,使PS系统和PL逻辑可以单独工作。另外板上有一个可编程的时钟芯片SI5338P为高速收发器GTX提供差分时钟源。

2.3、复位按键(参考20课)

板卡上有1个复位按键RESET和1个用户按键。复位信号连接到ZYNQ芯片PS复位管脚上,用户可以使用这个复位按键来复位ZYNQ系统,1个用户按键是连接到PL的IO上。复位按键和用户按键都是低电平有效,复位按键和用户按键的连接示意图如下图所示:

2.4、JTAG接口(参考31课)

USB下载器连接PC和JTAG接口进行FPGA的调试JTAG线插拔的时候注意不要热插拔。

2.5、QSPI Flash(参考22课)

2.6、eMMC Flash(参考27课)

2.7、DDR3(参考23课)

2.8、USB转串口(参考7课)

2.9、千兆以太网接口(参考2课)

2.10、USB 2.0 OTG接口(参考37课)

2.11、pcie金手指(参考47课)

2.12、温度传感器 (参考11课)

2.13、SD卡槽(参考8课)

2.14、FMC连接器(参考56课)

2.15、风扇(参考12课)

2.16、LED灯(参考42课)

2.17、SMA接口

2.18、电源接口

3、基于ZYNQ的FPGA硬件设计注意事项(★)

3.1、FPGA中Config0的相关管脚设置

3.1.1、相关管脚

| CFGBVS_0 |

VCCO_0电压为3.3V/2.5V时,CFGBVS为高电平,即接到VCCO_0; VCCO_0电压为1.8V/1.5V时,CFGBVS为低电平,即接到GND。 |

| PROGRAM_B_0 |

低电平有效复位配置逻辑。当PROGRAM_B脉冲为低电平时,FPGA配置被清零并启动新的配置序列。 在下降沿启动配置复位,并且配置(即编程)序列在随后的上升沿开始。为了确保输入稳定的高电平,需要外部连接一个≤4.7kΩ的电阻到VCCO_0。 |

| INIT_B_0 |

配置存储器的初始化(低电平有效); 当FPGA处于配置复位状态,FPGA正在初始化(清除)其配置存储器时,或者当FPGA检测到配置错误时,FPGA将此引脚驱动为低电平。完成FPGA初始化过程后,INIT_B释放到高阻态,此时外部电阻预计将INIT_B拉高。 在上电期间,INIT_B可以在外部保持低电平,以在初始化过程结束时停止上电配置序列。 当初始化过程后在INIT_B输入检测到高电平时,FPGA继续执行M [2:0]引脚设置所指示的配置序列的其余部分。 将INIT_B连接至一个≤4.7kΩ的上拉电阻至VCCO_0,以确保从低到高的转换。 |

| DONE_0文章来源:https://www.toymoban.com/news/detail-838528.html |

DONE表示配置成功完成(高电平有效)作为输出,这个引脚说明配置过程已经完成;作为输入,配置为低电平可以延迟启动。文章来源地址https://www.toymoban.com/news/detail-838528.html |

3.1.2、VCCADC_0、GNDADC_0 (XADC模块)

3.1.3、TCK_0、TDI_0、TDO_0、TMS_0 (JTAG)

3.2、BOOT配置---拨码开关配置

3.3、FPGA与外设电平匹配(★)

3.4、FPGA中HP的DCI功能(★)

3.5、FPGA 的高速MGTx电路设计注意点

3.5.1、MGTAVCC的电平

3.5.2、端接校准电阻

3.5.3、AC耦合电容

详细内容参考视频讲解

到了这里,关于S7---FPGA- ZYNQ7100板级原理图硬件实战的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!