1 Master BPI配置信号

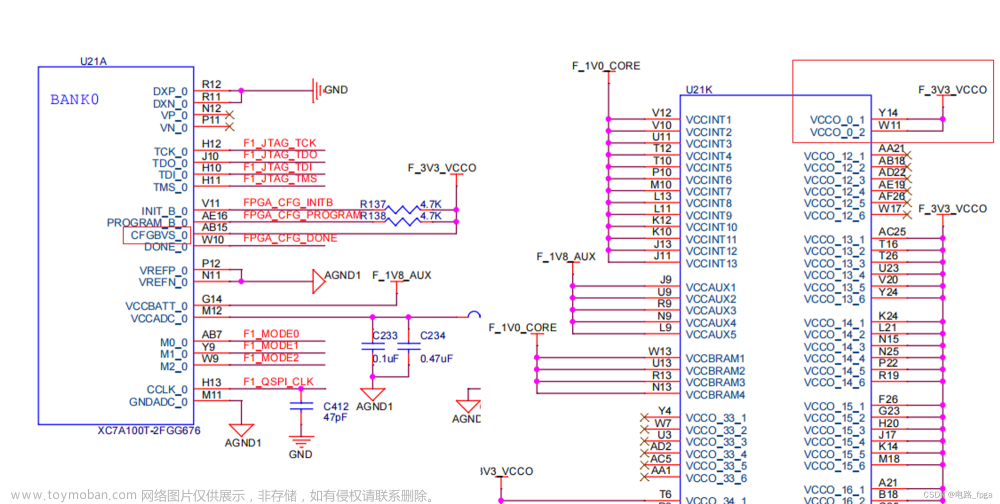

主BPI配置模式用于对启动加载时间有要求的情况下使用,因为BPI模式为并行加载,加载时间较短,适用于需要快速加载的场景;主BPI模式,M[2:0] = 3’b010。主BPI模式进行读写操作时,分为同步与异步两种,对于同步读取,FPGA的CCLK管脚输出必须连接到Flash的CLK引脚;对于异步读取,FPGA的CCLK不连接,直接悬空。BPI Flash其所需要的专用部分配置接口如下所示。表2-5 主BPI模式 BPI Flash配置管脚连接

Flash Pin 连接方式

WP# 写保护信号:通过4.7K电阻直接上拉到VCCO_0。

RST# 复位信号:与FPGA的INIT_B直接相连,并通过4.7K电阻上拉到VCCO_0。

WE# 写使能:与FPGA的FEW_B直接相连,并通过4.7K电阻上拉到VCCO_0。

OE# 输出使能:与FPGA的FOE_B直接相连,并通过4.7K电阻上拉到VCCO_0。

A[n:1] 地址线:与FPGA的A[28:0]直接相连。A[0]对A[0]。

CLK 时钟线:如果为异步读写,CLK直接接地;如果为同步读写,直接与FPGA CCLK相连。

ADV# 地址有效信号:异步读写直接接地,同步文章来源地址https://www.toymoban.com/news/detail-840772.html

文章来源:https://www.toymoban.com/news/detail-840772.html

到了这里,关于Xilinx(AMD) 7系列FPGA——主BPI配置模式的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!