笔者之前主要是使用c语言和matab 进行编程,从2024年年初开始接触verilog,通过了一周的学习,基本上对verilog 的语法有了基本认知。总统来说,verilog 的语法还是很简单的,主要难点是verilog是并行运行,并且强烈和硬件实际电路相关,在设计到的时候需要考虑时序问题和可综合问题。

时序问题:因为verilog 是基于硬件实现,在实现的时候要考虑到硬件电路的建立时间和稳定时间,所以会遇到锁存器。并且在多个并行的运算在耦合到一起时,需要考虑时序。

可综合:指的是是否可以生成对应的电路,如果一段程序无法生成对应的电路,那么这个程序可能只能进行仿真,最后实际无法在硬件上实际运行。

基本设计单元

对于c语言中一个最基本的设计单元称为函数

void functionname(parameter)

{

funtion description

}

对于verilog 基本设计单元则称为模块,结构也类似

module block(parameter)

block desription

endmodule

具体实例:

module test(a,b,c,d)

input a,b,c;// 可以在block 内部进行输入输出定义 这里没有指明为宽 则默认a,b,c,d 宽带为1bit

output d;

assign d=a|b|c; // 这里 是对输入的三个信号线 abc 进行按位求或,主要有一个问题高电平,则输出d为高电平

endmodule

如果输入输出的数据位宽不为1,可以按照如下方式进行定义

input [信号位宽-1:0] 端口名字1;

output[信号位宽-1:0] 输出端口名字;

inout[信号位宽-1:0] 端口名字;// 这个端口即是输入端口又是输出端口

数据定义

数字表现形式

数子常用的表现形式包括二进制十进制和十六进制,下面展示了用不同进制表示一个字为10

二进制 4'b1010;

十进制 4’d10;

十六进制 4‘hA;

如果直接写10,则默认是十进制。

对于负数则如下表示:

二进制 -4'b1010;

十进制 -4’d10;

十六进制 -4‘hA;

对于c编程中一个bit只能有两种情况 true或者false 也即 1或者0.但是对于实际电路中出了0或者1 还有另外两个值,使用x表示不定值,使用z/?代表高阻值

如

二进制 4'b101z;

十进制 4’dz;

十六进制 4‘hx;

另外一个让我感觉verilog 很贴心的是增加了_ 来对数据进行分隔,从而提高可读性,

32’b1111_1110_0001_1101_1011_0011_0101_1101,

希望其他语言中也早点支持这种分隔符,有的时候真是数的让人眼花缭乱。

数据类型

verilog 中一共有19个数据类型,其中最常用的为wire,reg,integer和parameter。

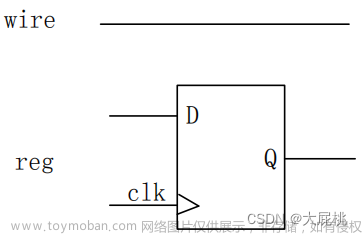

1. wire 数据类型 常用在表示以assign 关键字指定的组合逻辑信号,verilog 程序模块中输入和输出默认为wire 类型,wire 数据可以作为任何方程的输入,但是输出的时候需要用到assign

如

wire[3:0] b;

assign b=10;//定义了一个wire类型的b 并且给b赋值为10,注意 给wire 赋值的时候必须用assign。

2. reg型数据,register 是数据存储对象的抽象,通过赋值语句可以修改寄存器储存的数据,reg数据常和always 使用,

reg[3:0] b;

always*

b=10;

3. parameter 型数据是用来定义常量

module Test()

parameter b=7;// 定义了一个 参数 为7 这个参数可以通过上层的模块修改

........

endmodule

module Topfun()

Test #(10) testexample;//在这里实例化了Test 并且修改b=10

endmodule

运算符和表达式

verilog 中的运算符基本都和c语言中使用方法一致,唯有拼接运算符是一个新的。

reg [7:0] var1;

reg [15:0] var2;文章来源:https://www.toymoban.com/news/detail-841117.html

wire [22:0] combined = {var1, var2};// 通过拼接运算符把var1和var2 合并到了一起文章来源地址https://www.toymoban.com/news/detail-841117.html

到了这里,关于verilog 从入门到看得懂---verilog 的基本语法数据和运算的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[免费专栏] Android安全之Android Xposed插件开发,小白都能看得懂的教程](https://imgs.yssmx.com/Uploads/2024/02/491374-1.png)