简介

本章节是对于高速IO接口应用的一个扩展,目前扩展为CML。

CML(电流模式逻辑-即Current Mode Logic)。电路主要靠电流驱动,也是所有高速数据接口形式中最简单的一种,它的输入与输出的匹配集成在芯片内部,基本不需要外部端接,从而使单板硬件设计更简单、更简洁。CML其为LVDS的升级版本,但速度更快,速度最快可达到10G。

FPGA的高速IO接口GTX,可完美覆盖CML的速度范围。

应用

应用1:长距离传输视频数据;

应用2:传输高速数据。

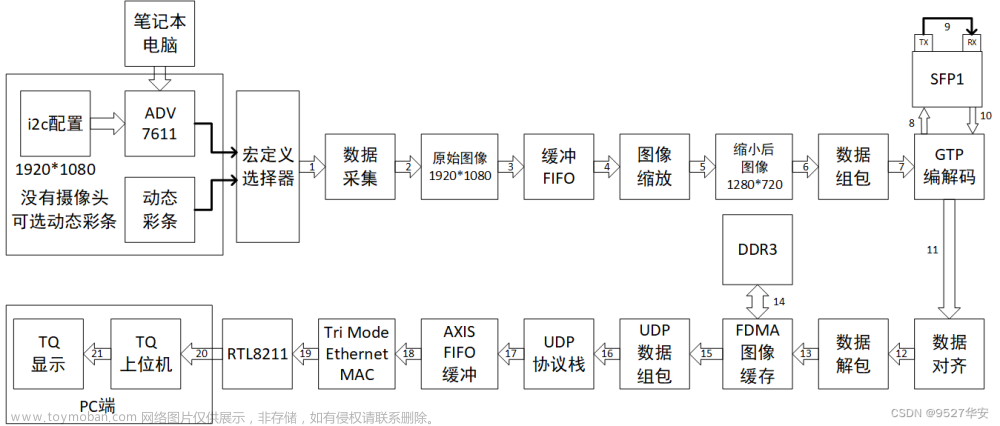

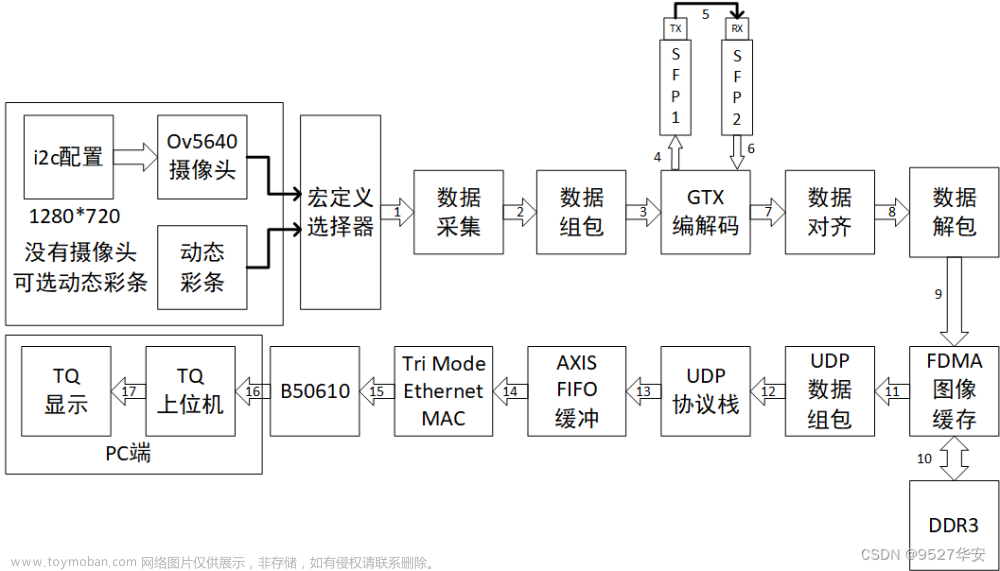

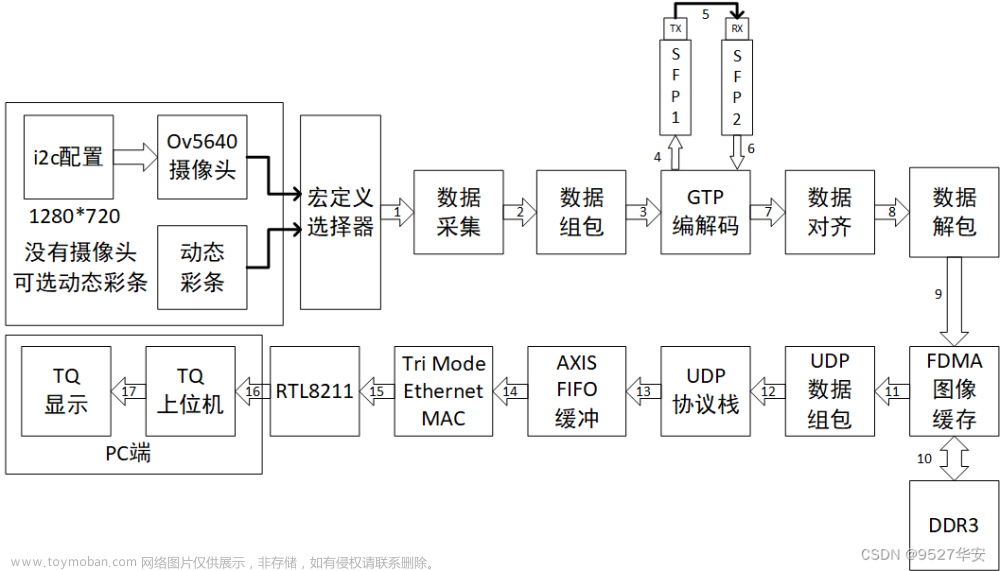

硬件框架

GTX实现物理层

文章来源:https://www.toymoban.com/news/detail-841307.html

文章来源:https://www.toymoban.com/news/detail-841307.html

CML采用3.75Gbps速度,基准时钟采用125Mhz。文章来源地址https://www.toymoban.com/news/detail-841307.html

到了这里,关于基于FPGA的视频接口之高速IO(CML)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!