1、概述

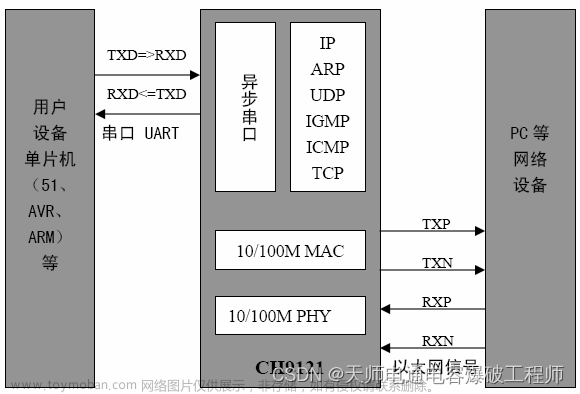

CH432芯片是一款扩展串口芯片,当你的MCU所带的串口不足时,可以通过此芯片来扩展出两个串口出来。

此芯片支持支持半双工收发自动切换、带自动硬件速率控制的高速串口、红外编解码、RS485、IrDA等等许多功能,本文只阐述简单串口功能的实现逻辑。

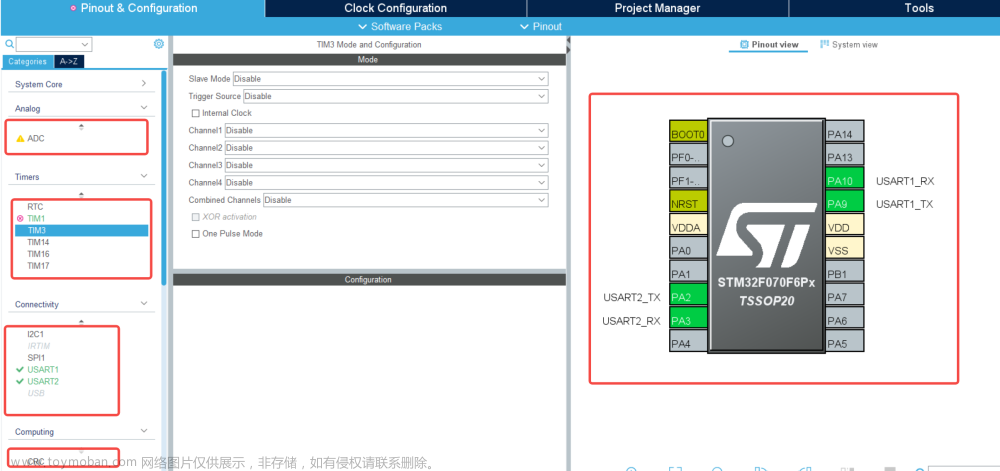

此芯片和MCU的通信方式包括8位并口和SPI方式,本文只阐述SPI方式的通信。

CH432手册将各种功能糅杂在一起,阅读非常费劲,本文来梳理一下通过SPI串口方式与MCU通信实现简单的双串口通信的过程,只针CH432T进行梳理。

2、特点

- 两个串口完全独立,互不影响,均为异步串口。

- 支持 5、6、7或者8个数据位以及1或者2个停止位。

- 支持奇、偶、无校验、空白0、标志1等校验方式。

- 可编程通讯波特率,支持 115200bps 以及最高达 4Mbps 的通讯波特率。

- 内置 16 字节的 FIFO 先进先出缓冲器,支持 4 个 FIFO 触发级。

- 支持全双工和半双工串口通讯,提供 RTS 串口发送状态信号支持 RS485 收发自动切换。

- 内置时钟振荡器,支持频率范围 0.9216MHz~32MHz 的晶体,默认使用 22.1184MHz 晶体。

- 3MB/24MHz 速度的 SPI 串行接口

- SPI 串行接口包含 SPI 片选、串行时钟、串行输入和输出,并且 SPI 输出与输入引脚可以并在一起,通过单线双向模式与SPI通信。

- 中断输出引脚是可选连接,低电平有效,可以通过查询寄存器中的中断标志位代替。

- 支持 5V 或者 3.3V 电源电压,支持串口低功耗睡眠模式。

3、引脚

3.1电源和系统信号相关引脚

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

|---|---|---|---|

| 18 | VCC | 电源 | 正电源端 |

| 3,19 | GND | 电源 | 公共接地端 |

| 9 | XI | 输入 | 晶体振荡的输入端,需要外接晶体及振荡电容 |

| 10 | XO | 输出 | 晶体振荡的反相输出端,需要外接晶体及振荡电容 |

| 12 | HLF# | 输入 | 半双工通讯模式使能,低电平有效,内置弱上拉电阻 |

3.2 与MCU相连的引脚

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

|---|---|---|---|

| 20 | SCK | 输入 | SPI 方式的 SPI 串行时钟输入 |

| 17 | SDI | 输入 | SPI 方式的 SPI 串行数据输入 |

| 16 | SDO | 三态输出 | SPI 方式的 SPI 串行数据输出 |

| 2 | SCS# | 输入 | SPI 方式的 SPI 片选输入,低电平有效 |

| 1 | INT# | 开漏输出 | 中断请求输出,低电平有效 |

3.3 串口1相关引脚

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

|---|---|---|---|

| 6 | RXD | 输入 | 异步串行数据输入,内置弱上拉电阻 |

| 5 | RTS | 输出 | 在半双工通讯时为串行数据正在发送状态指示,高有效 |

| 4 | TXD | 输出 | 异步串行数据输出 |

3.3 串口2相关引脚

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

|---|---|---|---|

| 13 | RXD1 | 输入 | 异步串行数据输入,内置弱上拉电阻 |

| 15 | RTS1 | 输出 | 在半双工通讯时为串行数据正在发送状态指示,高有效 |

| 11 | TXD1 | 输出 | 异步串行数据输出 |

4、半双工配置

CH432芯片支持全双工模式和半双工模式。

HLF#引脚控制芯片以半双工或全双工模式运行。HLF#高电平时,全双工模式运行,低电平情况下以半双工模式运行。

HLF#引脚内置弱上拉电阻,所以在HLF#引脚悬空情况下,默认其上电平为高电平。

在半双工串口应用中,RTS 引脚(串口 1 则是 RTS1 引脚)用于串行数据正在发送状态指示,高电平有效,可以用于自动控制RS485 收发器的收发切换。

5、内部时钟

CH432 芯片内部具有时钟振荡器,只需要在 XI 和 XO 引脚之间连接一个晶体,并且分别为 XI 和XO 引脚对地连接振荡电容,就能产生串口所需的外部时钟信号,如果不接晶体和电容,CH432 芯片也可以通过 XI 引脚从外部时钟源直接输入时钟。

默认的外部时钟频率应该时1.4832MHz,对应的最应的最大串口波特率是115200bps。

串口1的IER(Interrupt Enable Register 中断使能寄存器)寄存器的位5 CK2X控制XI引脚的外部时钟信号的1/12分频或2倍频,产生的时钟信号提供给两个串口。CK2X默认为零情况下,外部时钟频率为1.4832MHz时,对应的最应的最大串口波特率是115200bps。

6、寄存器

因为CH432有两个串口,所以其每个串口均有一组相同的寄存器,每组寄存器共有8个,共有2组。串口1的寄存器从地址00H开始,直007H,串口2的寄存器从地址08H开始,直0FH。

在读写寄存器时,具体读写的是哪个寄存器由寄存器地址、LCR寄存器中的DLAB位和读写属性共同决定的。

如寄存器下表所示,表中 DLAB 为寄存器 LCR 的位 7,X 表示不关心 DLAB 值,RO 表示寄存器只读,WO 表示寄存器只写,R/W 表示寄存器可读可写。

若读写属性位RO,DLAB=0,寄存器地址为0,则读取的是RBR寄存器中的值;若读写属性位WO,DLAB=0,寄存器地址为0,则是给THR寄存器中写值;若读写属性位R/W,DLAB=1,寄存器地址为0,则是读取DLM的值或者给DLM写值。

| 寄存器 1地址 |

寄存器 2地址 |

DL AB |

R/W | 名称 | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 08 | 0 | WO | THR | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0 |

| 0 | 08 | 0 | RO | RBR | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0 |

| 1 | 09 | 0 | R/W | IER | RESET | LOWPOWER | SLP/CK2X | 0 | IEMODEM | IELINES | IETHRE | IERECV |

| 2 | 0A | X | RO | IIR | FIFOENS | FIFOENS | 0 | 0 | IID3 | IID2 | IID1 | NOINT |

| 2 | 0A | X | WO | FCR | RECVTG1 | RECVTG0 | 0 | 0 | 0 | TFIFORST | RFIFORST | FIFOEN |

| 3 | 0B | X | R/W | LCR | DLAB | BREAKEN | PARMODE1 | PARMODE0 | PAREN | STOPBIT | WORDSZ1 | WORDSZ0 |

| 4 | 0C | X | R/W | MCR | 0 | 0 | AFE | LOOP | OUT2 | OUT1 | RTS | DTR |

| 5 | 0D | X | RO | LSR | RFIFOERR | TEMT | THRE | BREAKINT | FRAMEERR | PARERR | OVERR | |

| 6 | 0E | X | RO | MSR | DCD | RI | DSR | CTS | △DCD | △RI | △DSR | △CTS |

| 7 | 0F | X | R/W | SCR | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0 |

| 0 | 08 | 1 | R/W | DLL | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0 |

| 1 | 09 | 1 | R/W | DLM | 位 15 | 位 14 | 位 13 | 位 12 | 位 11 | 位 10 | 位 9 | 位 8 |

6.1 RBR寄存器——Receview Buffer Register(接收缓冲寄存器)

LSR(Line Status Register 线路状态寄存器)的DATARDY位置为1则表示数据已经准备好。 当DATARDY = 1时,可以从RBR寄存器读取串口接收到的数据

如果FCR(FIFO Control register)寄存器的位1 FIFOEN=1 ,则从串口移位寄存器 RSR 接收到的数据首先被存放于接收 FIFO 中,然后通过该寄存器读出。

6.2 THR寄存器——Transmit Hold Register(发送保持寄存器)

发送保持寄存器,包括发送 FIFO,用于写入准备发送的数据。

如果FCR(FIFO Control register)寄存器的位1 FIFOEN=1 , 则写入的数据首先被存放于发送 FIFO 中,然后通过发送移位寄存器 TSR 逐个输出。

6.3 IER——Interrupt Enable register(中断使能寄存器)

| 寄存器位 | 名称 | 意义 |

|---|---|---|

| 7 | RESET | 该位置 1 则软复位该串口,该位能够自动清 0,无需软件清 0。 |

| 6 | LOWPOWER | 该位为 1 则关闭该串口的内部基准时钟,从而使该串口进入低功耗状态。 |

| 5 | SLP/CK2X | 串口 0 与串口 1 的该位用途不同,串口 0 是 SLP,该位为 1 则关闭时钟振荡器,从而使串口 0 与串口 1 全部进入睡眠状态,串口 1 是 CK2X,该位为 1 则强制将外部时钟信号 2 倍频后作为串口 0 和串口 1 的内部基准时钟。 |

| 4 | IEMODEM | 该位为 1 则允许调制解调器输入状态变化中断。 |

| 2 | IELINES | 该位为 1 则允许接收线路状态中断。 |

| 1 | IETHRE | 该位为 1 则允许发送保持寄存器空中断。 |

| 0 | IERECV | 该位为 1 则允许接收到数据中断。 |

6.4 IIR——Interrupt Identify register(中断识别寄存器)

所谓中断识别寄存器, 即为中断状态寄存器,显示生成的中断到底时哪一个。

FIFOENS:该位为 FIFO 启用状态,为 1 表示已经启用 FIFO。

| IID3 | IID2 | IID1 | NOINT | 优先级 | 中断类型 | 中断源 | 清中断方法 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 无 | 没有中断产 | 没有中断 | |

| 0 | 1 | 1 | 0 | 1 | 接收线路状态 | OVERR、PARERR、FRAMEERR、BREAKINT | 读 LSR |

| 0 | 1 | 0 | 0 | 2 | 接收数据可用 | 接收到的字节数达到 FIFO 的触发点 | 读 RBR |

| 1 | 1 | 0 | 0 | 2 | 接收数据超时 | 超过 4 个数据的时间未收到下一数据 | 读 RBR |

| 0 | 0 | 1 | 0 | 3 | THR 寄存器空 | 发送保持寄存器空,IETHRE 从 0 变 1 可以重新使能中断 | 读 IIR或写 THR |

| 0 | 0 | 0 | 0 | 4 | MODEM 输入变化 | △CTS、△DSR、△RI、△DCD | 读 MSR |

6.5 FCR——FIFO Control Register(FIFO控制寄存器)

主要用于复位和使能FIFO.

RECVTG1 和 RECVTG0设置接收 FIFO 的中断的触发点。功能如下:

| RECVTG1 | RECVTG0 | 功能 |

|---|---|---|

| 0 | 0 | 接收满 1 个字节产生接收数据可用的中断 |

| 0 | 1 | 接收满 4 个字节产生接收数据可用的中断 |

| 1 | 0 | 接收满 8 个字节产生接收数据可用的中断 |

| 1 | 1 | 接收满 14 个字节产生接收数据可用的中断 |

TFIFORST:该位置 1 则清空发送 FIFO 中的数据(不含 TSR),该位能够自动清 0,无需软件清 0。

RFIFORST:该位置 1 则清空接收 FIFO 中的数据(不含 RSR),该位能够自动清 0,无需软件清 0。

FIFOEN:该位为 1 则启用 FIFO,该位清 0 则禁用 FIFO,禁用 FIFO 后,相当于 FIFO 只有一个字节。

6.6 LCR——Line Control Register(线路控制寄存器)

DLAB:该位为除数锁存器存取使能,为 1 时才能存取 DLL 和 DLM,为 0 时才能存取 RBR/THR/IER。

BREAKEN:该位为 1 则强制产生 BREAK 线路间隔。

PARMODE1 和 PARMODE0:当 PAREN 为 1 时设置奇偶校验位的格式:00 则奇校验,01 则偶校验,10则标志位(MARK,置 1),11 则空白位(SPACE,清 0)。

PAREN:该位为 1 则允许发送时产生和接收时校验奇偶校验位,为 0 则无奇偶校验位。

STOPBIT:该位为 1 则两个停止位,为 0 则一个停止位。

WORDSZ1 和 WORDSZ0:设置字长度,00 则 5 个数据位,01 则 6 个数据位,10 则 7 个数据位,11则 8 个数据位。

6.7 LSR——Line Status Register(线路状态寄存器)

主要用来查询方式分析串口状态

| 位 | 名称 | 功能 |

|---|---|---|

| 7 | RFIFOERR | 该位为 1 表示在接收 FIFO 中存在至少一个 PARERR、FRAMEERR 或 BREAKINT 错误。 |

| 6 | TEMT | 该位为 1 表示发送保持寄存器 THR 和发送移位寄存器 TSR 全空。 |

| 5 | THRE | 该位为 1 表示发送保持寄存器 THR 空。 |

| 4 | BREAKINT | 该位为 1 表示检测到 BREAK 线路间隔。 |

| 3 | FRAMEERR | 该位为 1 表示正在从接收 FIFO 中读取的数据的帧错误,缺少有效的停止位。 |

| 2 | PARERR | 该位为 1 表示正在从接收 FIFO 中读取的数据的奇偶校验错。 |

| 1 | OVERR | 该位为 1 表示接收 FIFO 缓冲区溢出。 |

| 0 | DATARDY | 该位为 1 表示接收 FIFO 中有接收到的数据,读取 FIFO 中所有数据后,该位自动清 0。 |

6.8 DLL 和 DLM——波特率除数锁存器

DLL 是低字节,DLM 是高字节,两者组成的 16 位除数用于由 16 位计数器构成的串口波特率产生器。

该除数 = 串口内部基准时钟 / 16 / 所需通讯波特率。

如果串口内部基准时钟为 1.8432MHz,所需波特率为 9600bps,则除数=1843200/16/9600=12。

7、 中断操作

CH432T有一个中断引脚INT#,INT#引脚是低电平有效的开漏输出引脚,连接单片机时可能需要外加上拉电阻,在逻辑功能上是当串口1和2只要其中任何一个有中断请求产生,则INT#引脚输出低电平,否则 INT#引脚不输出。

两个串口合用一个中断请求,那么单片机在进入中断服务程序后,首先应该分析出是哪个串口的中断请求。。当进入中断服务程序后,单片机首先读取串口 0 的 IIR 寄存器,有中断则处理并退出,无中断则读取串口 1 的 IIR 寄存器,有中断则处理并退出,无中断则直接退出。当确认是某个串口的中断后,如果有必要还可以进一步分析 LSR 寄存器,分析中断原因并处理。

如果串口工作于中断方式,那么需要设置 IER 寄存器以允许相应的中断请求,并设置 MCR 寄存器

中的 OUT2 以允许中断输出。

8、查询操作

如果串口工作于查询方式,那么无需设置 IER 和 MCR 的 OUT2,只需查询 LSR 寄存器的相关状态位并分析处理。

在查询方式下,单片机可以根据 LSR 寄存器的 THRE 位判断发送 FIFO 是否为空,THRE 为 1 则可

以向 THR 寄存器及 FIFO 写入数据,如果使能 FIFO,那么一次可以写入最多 16 个字节。

在查询方式下,单片机可以根据 LSR 寄存器的 DATARDY 位判断接收 FIFO 是否为空,DATARDY 为 1

则可以从 RBR 寄存器读取一个字节的数据,然后查询 DATARDY 位的状态,如果有效则再次读取 RBR 寄

存器,直到 DATARDY 位为 0。

9、串口操作

如果设置FCR寄存器的FIFOEN位为 1,则从串口移位寄存器 RSR 接收到的数据首先被存放于接收 FIFO 中,然后通过该寄存器读出。可以向 THR 寄存器及FIFO 一次写入最多 16 个字节,由 CH432 按顺序自动发送。如果禁止 FIFO,那么一次只能写入一个字节。如果没有数据需要发送,那么可以直接退出(之前读取 IIR 时已经自动清除中断)。

串口发送的保持寄存器 THR 空中断(IIR 寄存器的低 4 位为 02H)是指发送 FIFO 空。当读取 IIR

寄存器后,该中断被清除,或者当向 THR 写入下一个数据后,该中断也能被清除。如果仅仅是向 THR

写入一个字节,那么由于该字节很快被转移到发送移位寄存器 TSR 中开始发送,所以 CH432 很快会再

次产生发送保持寄存器 THR 空中断的请求,此时可以写入下一个准备发送的数据。当 TSR 寄存器中的

数据被全部移出后,串口发送才真正完成,此时 LSR 寄存器的 TEMT 位变为 1 有效。

如果设置FCR寄存器的FIFOEN位为 1,则写入的数据首先被存放于发送 FIFO 中,然后通过发送移位寄存器 TSR 逐个输出。

串口接收的数据可用中断(IIR 寄存器的低 4 位为 04H)是指接收 FIFO 中的已有数据字节数已经达到或超过由 FCR 寄存器的 RECVTG1 和 RECVTG0 选择的 FIFO 触发点。当从 RBR 读取数据使 FIFO 中字节数低于 FIFO 触发点时,该中断被清除。当接收 FIFO 全空时,LSR 寄存器的 DATARDY位为 0,当接收 FIFO 中有数据时,DATARDY 位为 1 有效。

串口接收的数据超时中断(IIR 寄存器的低 4 位为 0CH)是指接收 FIFO 中至少有一个字节的数据,并且从上一次串口接收到数据和从上一次被单片机取走数据开始,已经等待了相当于接收 4 个数据的时间。

当单片机收到串口接收数据超时的中断后,可以先从 RBR 寄存器读取一个字节,然后查询 LSR 寄存器的 DATARDY 位,如果 DATARDY 位有效则再读取一个字节,直到 DATARDY 位无效。

当单片机收到串口接收数据可用的中断后,可以先从 RBR 寄存器读取由 FCR 寄存器的 RECVTG1 和

RECVTG0 设定的字节数,然后再查询 LSR 寄存器的 DATARDY 位,如果 DATARDY 位有效则再读取一个字

节,直到 DATARDY 位无效,或者全部是通过查询 LSR 寄存器的 DATARDY 位有效后再读取。

接收线路状态中断(IIR 寄存器的低 4 位为 06H)是指上次单片机读取 LSR 寄存器之后,CH432在串口接收过程中检测到错误或者异常。当从 LSR 寄存器读取线路状态后,该中断及 LSR 寄存器中的状态位被清除。该中断是 LSR 寄存器的位数据 BREAKINT、FRAMEERR、PARERR 和 OVERR 的逻辑“或”。

10、SPI接口

SPI 同步串行接口信号线包括:SPI 片选输入引脚 SCS#、串行时钟输入引脚 SCK、串行数据输入引脚 SDI 和串行数据输出引脚 SDO。

CH432 芯片的 SCS#引脚由单片机的 SPI 片选输出引脚或者普通输出引脚驱动,SCK 引脚由单片机的 SPI 时钟输出引脚 SCK 驱动,SDI 引脚由单片机的 SPI 数据输出引脚 SDO 或 MOSI 驱动,SDO 引脚则连接到单片机的 SPI 数据输入引脚 SDI 或 MISO。

对于硬件 SPI 接口,建议 SPI 设置是 CPOL=CPHA=0或者 CPOL=CPHA=1,并且数据位顺序是高位在前 MSB first。

CH432 总是从 SPI 时钟 SCK 的上升沿输入数据,并在允许输出时从 SCK 的下降沿输出数据,数据位顺序是高位在前,计满 8 位为一个字节。

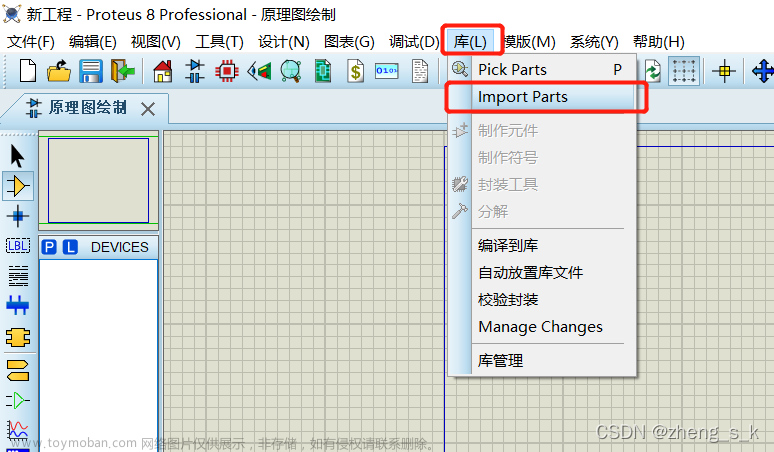

10.1 SPI写操作流程

(1)单片机产生 CH432 芯片的 SPI 片选,低电平有效;

(2)单片机按 SPI 输出方式发出一个字节的地址码,用于指定操作地址和读写操作方向,其位 1为数据传输方向,为 1 则写操作,位 5~位 2 指定当前操作地址。

(3)单片机发出一个字节的待写数据,CH432 收到并保存到指定地址

(4) 单片机禁止 CH432 芯片的 SPI 片选,以结束当前 SPI 操作。文章来源:https://www.toymoban.com/news/detail-842714.html

10.2 SPI读操作流程

(1)单片机产生 CH432 芯片的 SPI 片选,低电平有效;

(2)单片机按 SPI 输出方式发出一个字节的地址码,用于指定操作地址和读写操作方向,其位 1为数据传输方向,为 0 则读操作转,位 5~位 2 指定当前操作地址。

(3)CH432 从指定地址读出一个字节数据并输出,单片机收到数据并保存

(4) 单片机禁止 CH432 芯片的 SPI 片选,以结束当前 SPI 操作。文章来源地址https://www.toymoban.com/news/detail-842714.html

到了这里,关于CH432双串口芯片的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!