EBU6335 2022/23

Question 1

a) Describe entry in the context of digital system design. Also explain how VHDL is used in the entry

process.

[5 marks]

b) The following is an incomplete VHDL model the so-called Or-And-Invert (OAI) gate (Boolean function Y = (A + B) · C), possibly with some syntax errors.

[8 marks]

entity OAI21 is

port (

A B C: in std_logic

Y: out std_logic

)

end

architecture is

Y = ~(A + B * C)

end architecture

i) Copy, correct and complete the VHDL code.

(5 marks)

ii) Suggest the output of the gate if inputs are A = 0, B = C = 1.

(3 marks)

c) In a signed binary addition S = A + B, it is known that A > 0 and B < 0.

[10 marks]

i) Explain whether there will be a carry in such an addition or not.

(3 marks)

ii) How is signed number represented?

(2 marks)

iii) Suppose the following full adder block FA is given as a component, write the VHDL architecture (no

need to provide the entity) for a 48-bit binary subtractor that takes A and B and gives S. You can

ignore carry in and out for your answer.

entity FA is

port (X, Y, Cin : in std_logic;

S, Cout : out std_logic);

end FA;

(5 marks)

Page 2 of 8

EBU6335 2022/23

Question 2

a) Explain briefly how a D flip-flop can be constructed using D latch(es).

[4 marks]

b) Figure 1 shows a sequential block constructed by a 2-to-1 multiplexer (MUX) and a positive-edge

trigged D flip-flop. This can be used to build a shift register.

[11 marks]

Figure 1: Sequential Block built by a MUX and a Flip-flop

i) If it is given that inverter has an area of 2 units and any 2-input logic gate has an area of 3 units,

estimate the area of the block.

(3 marks)

ii) Design and construct a 4-bit left shift register (i.e. towards MSB) using the block in Figure 1:

input(s): shift in bit X, shift control Shif t (active-high)

output(s): counter outputs Y = (MSB)Y3Y2Y1Y0(LSB)

Illustrate your design using a diagram (with proper annotations)

(5 marks)

iii) Is your design in ii) synchronous? Explain why.

(3 marks)

c) You are asked to design an add-2 synchronous counter that counts in 0, 2, 4,... numerically.

[8 marks]

i) Discuss a general strategy to design a synchronous counter

(4 marks)

ii) Write the VHDL architecture for the required add-2 synchronous counter with an asynchronous reset,

based on the following entity.

Your answer should use NO components.

entity SyncCountBy2 is

port (RST: in std_logic; -- asynchronous reset

CLK: in std_logic; -- clock signal

Q: out std_logic_vector(7 downto 0));

end SyncCountBy2;

(4 marks)

Page 3 of 8

EBU6335 2022/23

Question 3

a) A mealy finite state machine is used to automate a vending machine. The machine dispenses a bottle

of water after ≥ (greater than or equal to) 1 Yuan (=10 Jiao) is deposited. There is a single slot

through which to insert Yuan and Jiao. One cannot insert Yuan and Jiao at the same time. One

cannot insert any other coins or notes. The machine does not issue change. Figure 2 shows the state

transition diagram for the system.

[10 marks]

Figure 2: State transition diagram for a vending machine which dispenses bottles of water

i) State one difference between a synchronous state machine and an asynchronous state machine?

(1 marks)

ii) How many flip-flops in minimum are required to implement this state machine?

(1 marks)

iii) Part of the VHDL code used to implement the state machine is given below. Complete the code.

(8 marks)

entity mealy is

Port ( clk, rst : in STD_LOGIC;

1_Yuan, 5_Jiao : in STD_LOGIC;

dispense_water : out STD_LOGIC);

end mealy;

architecture Behavioral of mealy is

type state is (st0, st1);

signal present_state , next_state: state;

begin

syncronous_process: process (clk)

begin

if rising_edge(clk) then

if (rst = '1') then

present_state <= st0;

else

present_state <= next_state;

end if;

end if;

end process;

next_state_and_output_decoder: process(present_state , din)

begin

dispense_water <= '0';

next_state <= present_state;

case (present_state) is

-- your answers begin here

Page 4 of 8

EBU6335 2022/23

-- ...

-- ...

end case;

end process;

end Behavioral;

b) Consider the incomplete first-in first-out (FIFO) buffer shown in Figure 3. The 4-bit up counter is included to generate full and empty control signals. Prepare the VHDL architecture without any component

for the part circled in red.

[7 marks]

Figure 3: Block diagram for a First-in first-out buffer

c) Consider the DRAM cell, shown in Figure 4.

Figure 4: DRAM cell

The following sequence of events occurs. Explain whether this will lead to a ‘1’ being stored in the

cell. If not please explain what changes/additions are required and why.

[3 marks]

Step 1: The row input is set to 5V to represent the ‘1’ that will be written to the cell.

Step 2: Next the transistor must be turned on by setting the row input to 5V.

Step 3: The voltage on the capacitor will then increase until it reaches 5V.

Step 4: The transistor must remain turned on in order to trap the stored charge.

Page 5 of 8

EBU6335 2022/23

d) Figure 5 shows a number of tristate logic gates connected to a common bus line. Copy the diagram

and add the missing inputs and outputs to the points labelled A, B, C on the diagram.

[3 marks]

Figure 5: Tristate logic circuit

Page 6 of 8

EBU6335 2022/23

Question 4

a) The following algorithm is used to compare two 5-bit binary numbers and count the number of

corresponding bits that differ between them.

[13 marks]

i=0

Number_of_Bits = 5

while (i < Number_of_Bits) {

i=i+1

if (Binary_Number_1(i) =/ Binary_Number_2(i)){

j=j+1

}

}

output = j;

You are given a datapath as shown in Figure 6. The control signals are circled with their respective

bit positions in the control word, e.g. LD for R0 is bit 1 of the control word. RX.0 denotes the bit 0

(LSB) of the value stored in register RX and the shifter shifts value exactly 1 bit to the left (towards

LSB).

Figure 6: A Datapath with 5 registers

i) Based on the datapath shown in Figure 6, express the algorithm in RTL/RTN. You should generate

a done signal when the algorithm finishes.

(7 marks)

ii) Derive the control words (13; 12; ... ; 1; 0) for your algorithm.

(6 marks)

b) Consider the following number 5.37510. Express this number using a 10-bit binary number having

same number of bits for the integer and fractional parts.

[4 marks]

c) We wish to form the following product: 710 ×310. Let M = 710 and Q = 310. Use Booth’s Algorithm

to calculate the result. Show all workings.

[6 marks]

Page 7 of 8

EBU6335 2022/23

Question 5

ASCII code is a character encoding using exactly eight bits. In digital communications for ASCII code,

a start bit S (1→ 0) and a stop bit P (0→ 1) are attached to the beginning and the end of the character bit

stream respectively. For example, character A is encoded and transmitted as S01000001P.

You are now required to build a digital system for communications for 8-bit ASCII code.

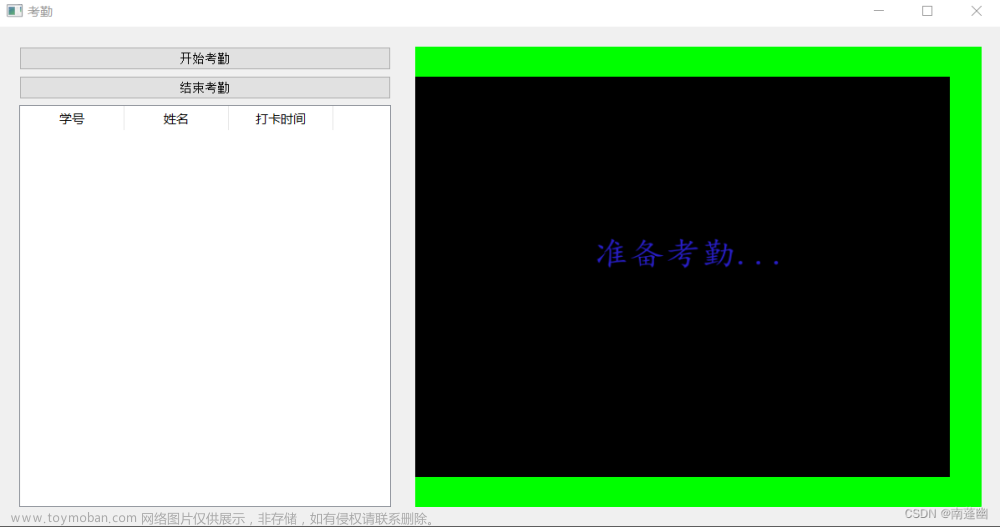

Based on your design experience from the course project, discuss your approach in (i) designing an asynchronous ASCII code transmitter and receiver, and (ii) modelling and implementing the WX:codehelp 文章来源地址https://www.toymoban.com/news/detail-842917.html

文章来源:https://www.toymoban.com/news/detail-842917.html

到了这里,关于EBU6335 digital system design的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!