-

微型计算机的硬件共性结构及基本性能指标

- 关于存储器的介绍

-

微型计算机的基本性能指标

- 1. 字长

- 2. 主频

- 3. 存储容量

- 4. 外设扩展能力

- 5. 软件配置情况

-

Arm Cortex 系列微处理器系列概述

- Arm Cortex-A 系列处理器

- Arm Cortex-R 系列处理器

- Arm Cortex-M 系列处理器

-

Cortex-M3 和 Cortex-M4简介

- 处理器类型

- 架构

- 指令集

- 模块框图

- 存储器系统

- 中断和异常支持

微型计算机的硬件共性结构及基本性能指标

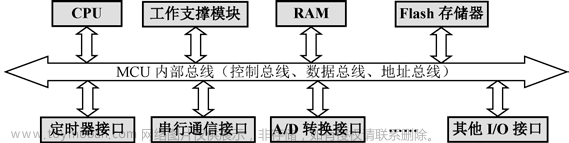

微型计算机的硬件共性结构可以简单地表述为:微型计算机是在内部集成了中央处理单元、存储器(RAM/ROM 等)、定时器/计数器及多种 I/O 接口的比较完整的数字处理系统。

关于存储器的介绍

随机存取存储器,也称为主存(内存),是可以和 CPU 直接进行数据交换的内部存储器,具有随时读写、速度快的特点,一般用于存储操作系统和其他正在运行的程序的临时数据。 RAM 在使用的过程中可以从任意指定的地址进行写入和读出操作,但它的数据保护性不够好,一旦断电,其所存储的数据就会消失。

Flash 存储器具有不易失性、电擦除、可在线编程、存储密度高、功耗低和成本低等特点。随着 Flash 技术的逐步成熟, Flash 存储器已经成为 MCU 的重要组成部分。 Flash 存储器的不易失性与磁存储器(MRAM)相似,不需要后备电源来保持数据。 Flash 存储器可在线编程,可取代电擦除可编程只读存储器(EEPROM),用于保存运行过程中的参数。对 Flash 存储器的读写不同于对一般 RAM 的读写,它需要专门的编程过程。 Flash编程的基本操作有两种:擦除(Erase)和写入(Program),擦除操作的含义是将存储单元的内容由二进制的 0 变成 1,而写入操作的含义是将存储单元的某些位由二进制的 1变成 0。

微型计算机的基本性能指标

1. 字长

字长是计算机内部一次可以处理的二进制数的位数,一般计算机的字长取决于它的通用寄存器、内存储器、 ALU 的位数和数据总线的宽度。目前,微型计算机的字长一般有 16 位、 32 位或 64 位。

2. 主频

主频是指微型计算机中 CPU 的时钟频率,也就是 CPU 运算时的工作频率。一般来说,主频越高,一个时钟周期内完成的指令数越多,当然 CPU 的速度也就越快。目前 CPU 的主频已达到 MHz、 GHz 级别。

3. 存储容量

存储容量是衡量微型计算机存储能力的一个指标,它包括内存容量和外存容量。内存容量由 CPU 的地址总线的位数决定,目前已达到 MB、GB 级别;外存容量主要是指硬盘(Hard Disk)容量,目前已达到 GB、 TB 级别。

4. 外设扩展能力

一台微型计算机可配置的外部设备的数量以及类型,对整个系统的性能有重大影响。如显示器的分辨率、多媒体接口功能和打印机型号等,都是外部设备选择中要考虑的问题。

5. 软件配置情况

软件配置情况直接影响微型计算机系统的使用和性能的发挥,通常应配置的软件有操作系统、计算机语言以及工具软件等,另外还可配置数据库管理系统和各种应用软件。

Arm Cortex 系列微处理器系列概述

Arm Cortex-A 系列处理器

Arm Cortex-A 系列是基于 Arm v7A 架构基础的处理器,面向尖端的基于虚拟内存的操作系统和用户应用。作为开放式操作系统的高性能的应用程序处理器, 在高级工艺节点中可实现高达 2GHz 及以上标准频率的卓越性能,从最新技术的移动 Internet 必备设备(如智能手机、移动计算平台、 超便携的上网计算机或智能计算机等)到汽车信息娱乐系统、 企业网络、打印机、服务器和下一代数字电视系统无处不在。 因而 Arm Cortex-A 系列处理器适用于具有高计算要求、运行丰富操作系统以及提供交互媒体和图形体验的应用领域。

Arm Cortex-R 系列处理器

Arm Cortex-R 系列是基于 Arm v7R 架构基础的处理器,面向实时系统的应用, 为具有严格的实时响应限制的嵌入式系统提供高性能计算解决方案。目标应用包括智能手机、硬盘驱动器、数字电视、医疗行业、工业控制、汽车电子等。 Arm Cortex-R 处理器是专为高性能、可靠性和容错能力而设计的,其行为具有高确定性,同时保持很高的能效和成本效益。

Arm Cortex-M 系列处理器

Arm Cortex-M 系列是基于 Arm v7M/v6M 架构基础的处理器,面向微控制器的应用, 是一系列可向上兼容的高能效、易于使用的处理器,这些处理器旨在帮助开发人员满足将来的嵌入式应用的需要。 Arm Cortex-M 系列针对成本、 功耗敏感的 MCU 和终端应用(如智能测量、 人机接口设备、汽车和工业控制系统、大型家用电器、消费性产品和医疗器械等)的混合信号设备进行优化。

Cortex-M3 和 Cortex-M4简介

处理器类型

ARM Cortex-M 为 32 位 RISC(精简指令集)处理器,其具有

- 32 位寄存器

- 32 位内部数据通路

- 32 位总线接口

Cortex-M3 和Cortex-M4 处理器都具有三级流水线(取指、译码和执行),它们都基于哈佛总线架构,取指令和数据访问可以同时执行。

ARM Cortex-M 处理器的存储器系统使用 32 位寻址,地址空间最大为 4GB。存储器映射是一致的,这就意味着尽管总线接口有多个,4GB存储器空间却只有一个。存储器空间包括程序代码、数据、外设以及处理器内的调试支持部件。

与其他任何 ARM 处理器相同,Cortex-M 处理器基于一种加载—存储架构。这也就意味着数据需要从存储器中加载和处理后,使用多个单独的指令写回存储器。例如, 要增加 SRAM 中存储的数据值,处理器需要使用一条指令从 SRAM 中读出数据,并且将数据放到处理器的寄存器中,然后使用第二条指令增加寄存器中的数据值,最后使用第三条指令将数值写回存储器。处理器内部的寄存器细节一般被称作编程模型。

架构

对于ARM处理器,架构一般指两个方面:

- 架构:指令集架构(ISA)、编程模型(对软件可见)以及调试方法(对调试器可见)

- 微架构:接口信号、指令执行时序以及流水线阶段等实现相关的细节,微架构为处理器设计相关的。

Cortex-M3 和Cortex-M4 处理器都基于ARMv7-M 架构。

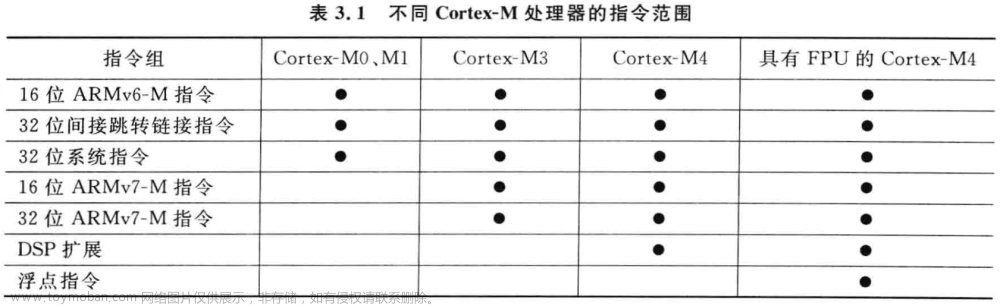

指令集

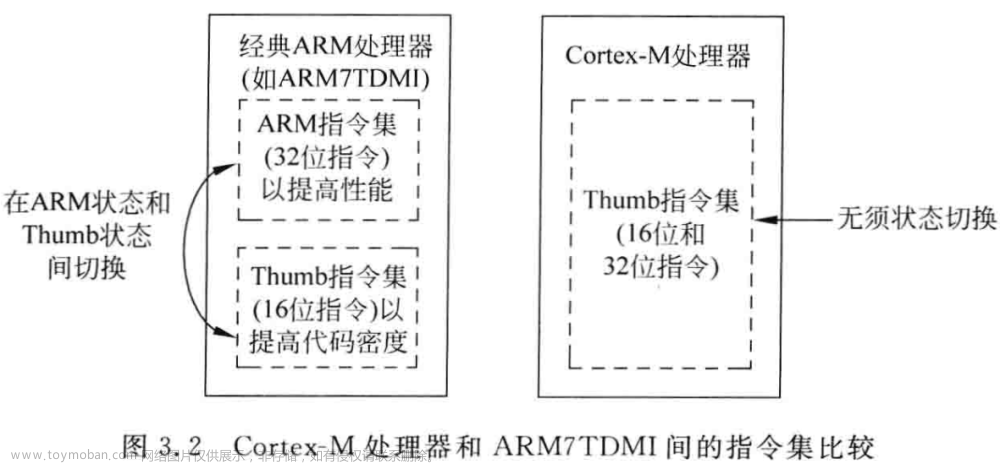

Cortex-M 处理器使用的指令集名为 Thumb(其中包括 16 位 Thumb 指令和更新的 32 位 Thumb 指令),Cortex-M3 和 Cortex-M4 处理器用到了 Thumb-2 技术,它允许 16 位和 32 位指令的混合使用,以获取更高的代码密度和效率。

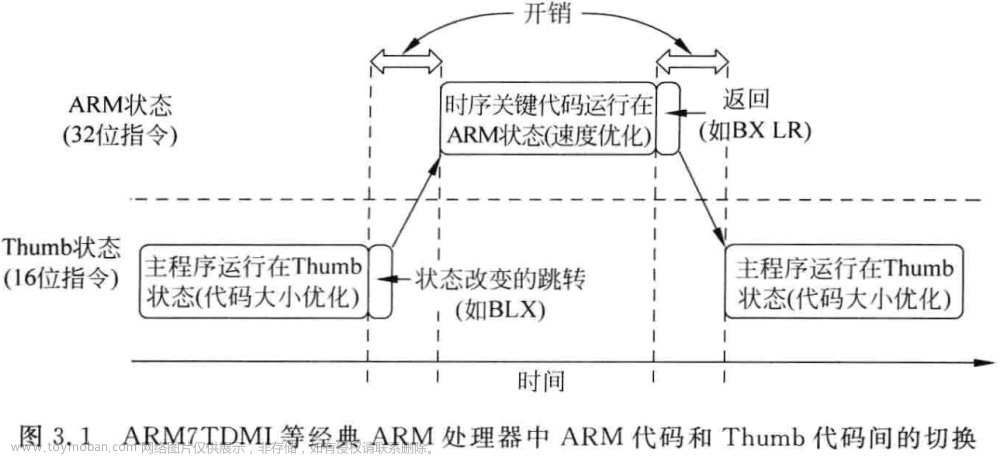

经典的 ARM 处理器:具有两种操作状态 32 位的 ARM 状态和 16 位的 Thumb 状态。在 ARM 状态中,指令是 32 位的,内核能够以很高的性能执行所有支持的指令;而对于 Thumb 状态,指令是 16 位的,这样可以得到很好的代码密度,不过 Thumb 指令却不具有ARM指令的所有功能,要完成特定的操作,可能需要更多的指令。中断处理是会进人 ARM 状态的。

要同时得到两者的优势,许多用于经典ARM处理器的应用程序混合使用了 ARM 和 Thumb 代码。不过这种混合编码的方式并不是非常理想,它会带来状态间切换的开销(执行时间和指令数),而且两个状态的分离还增加了软件编译过程的复杂度,对于不是很熟练的开发人员来说,优化代码更加困难。

Thumb-2 技术:Thumb 指令被扩展为支持 16 位和 32 位两种解码方式,无须在两个不同操作状态间切换就可以满足所有的处理需求。Cortex-M 处理器根本不支持 32 位的 ARM 指令,甚至中断处理都可以完全在 Thumb 状态中实现。

经典的 ARM 处理器相比,Cortex-M 处理器(Thumb-2 技术)优势:

- 无状态切换开销,节省执行时间和指令空间。

- 无须指定源文件中的 ARM 状态或 Thumb 状态,开发软件也更容易

- 在获得最佳的代码密度和效率的同时,还能很容易地达到高性能

- 利用 Thumb-2 技术,与 ARM 经典处理器相比,Thumb 指令集已经得到很大的扩展。注意,尽管所有的Cortex-M处理器都支持 Thumb-2 技术,它们实现的 Thumb ISA 子集不尽相同。

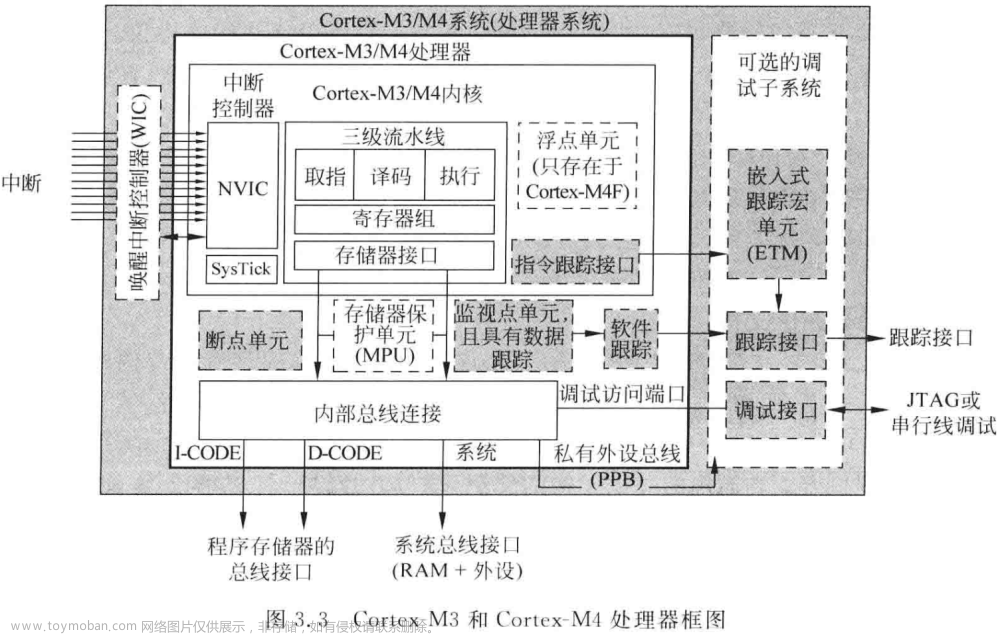

模块框图

从较高的层级来看,Cortex-M3 和 Cortex-M4 是非常相似的。尽管它们在内部数据通路设计上存在巨大差异,处理器的一些部分还是相似的,如取指缓冲、部分指令译码和执行阶段以及 NVIC。另外,“内核”层级外的部件基本上是相同的。Cortex-M3 和 Cortex-M4 处理器包含处理器内核、嵌套向量中断控制器(NVIC)、SysTick定时器以及可选的浮点单元(用于 Cortex-M4)。除了这些以外,处理器中还有一些内部总线系统、可选的存储器保护单元(MPU)以及支持软件调试操作的一组部件。内部总线连接可以将处理器和调试产生的传输送到设计的各个部分。

Cortex-M3 和 Cortex-M4 处理器是高度可配置的。例如,调试特性是可选的,若产品需要支持调试,片上系统设计人员可以将调试部件去掉,这样可以显著降低设计的硅片面积。有些情况下,芯片设计人员还可以选择降低硬件指令断点和数据监视点比较器的数量,以降低系统的门数量。许多系统特性也是可配置的,如中断输入的数量、支持的中断优先级的数量以及 MPU 等。

存储器系统

Cortex-M3 和 Cortex-M4 处理器本身并不包含存储器(没有程序存储器、SRAM或缓存),它们具有通用的片上总线接口,因此,微控制器供应商可以将它们自己的存储器系统添加到系统中。一般来说,微控制器供应商需要将下面的部件添加到存储器系统中:

- 程序存储器,一般是 Fash。

- 数据存储器,一般是 SRAM。

- 外设。

这样,不同微控制器产品可能会具有不同的存储器配置、不同的存储器大小和类型,以及不同的外设。

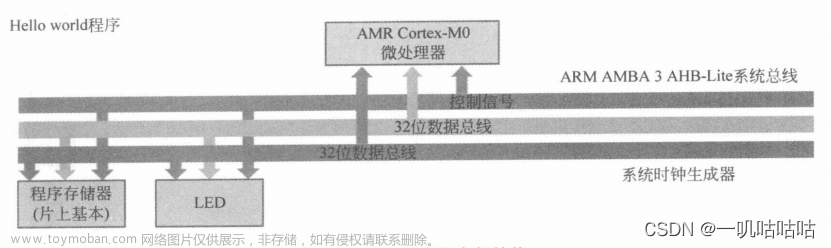

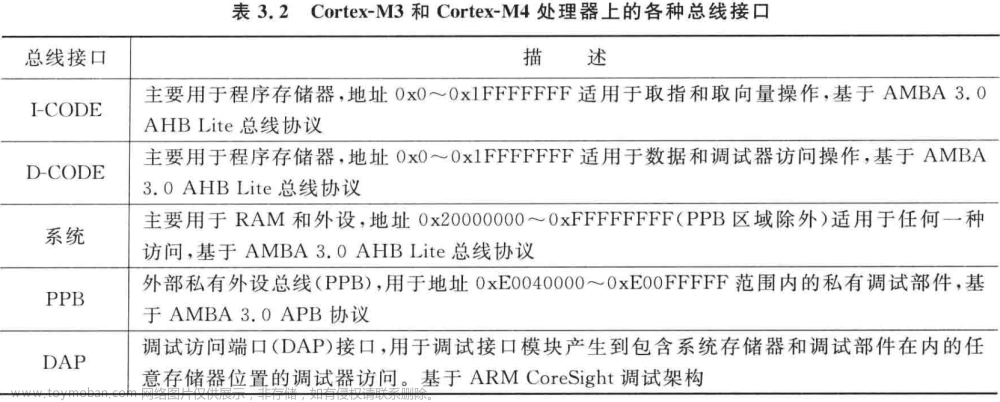

Cortex-M 处理器的总线接口为 32 位宽,且基于高级微控制器总线架构(AMBA)标准。AMBA 中包含多个总线协议,任何芯片设计者都可以免费使用这些标准协议。AMBA 规范可以从 ARM 网站下载。由于这些标准协议的低硬件成本、效率以及开放性,它们大受芯片设计者的欢迎。

Cortex-M3 和 Cortex-M4 处理器主要使用的总线接口协议为 AHBLite(高级高性能总线),它用于程序存储器和系统总线接口。AHBlite 协议为流水线结构的总线协议,可以在低硬件成本下实现高运行频率。高级外设总线(APB)接口为处理器使用的另外一种总线协议,它通常用于基于ARM的微控制器的总线系统。另外,APB协议在Cortx-M3和Cortex-M4处理器内部还用于调试支持。

与片外总线协议不同,AHBLite 和 APB 协议相对简单。这是因为芯片内的硬件配置是固定的,无须一种复杂的初始化协议来处理可能的配置(例如,无须支持类似于计算机技术中的“热插拔”)。

中断和异常支持

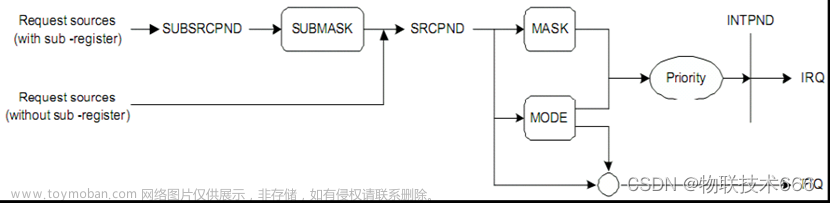

Cortex-M3 和 Cortex-M4 处理器中存在一个名为嵌套向量中断控制器(NVIC)的中断控制器,它是可编程的且其寄存器经过了存储器映射。NVIC 的地址固定,而且 NVIC 的编程模型对于所有的 Cortex-M 处理器都是一致的。

除了外设和其他外部输入的中断外,NVIC 还支持多个系统异常,其中,包括不可屏蔽中断(NMI)和处理器内部的其他异常源。文章来源:https://www.toymoban.com/news/detail-843765.html

Cortex-M3 和Cortex-M4 处理器是可配置的,微控制器供应商能够决定 NVIC 设计实际支持的可编程中断优先级的数量。尽管 NVIC的一些细节在不同的 Cortex-M3/M4 处理器间可能存在差异,中断/异常的处理和 NVIC 的异常模型却是相同的,它们定义在架构参考手册中。文章来源地址https://www.toymoban.com/news/detail-843765.html

到了这里,关于嵌入式笔记1.1 ARM Cortex-M3M4简介的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!