视频链接

FPGA-K7板级电源硬件实战01_哔哩哔哩_bilibili

FPGA-K7板级电源硬件实战

- 基于K7 板级的系统框图

2、基于K7 板级的电源设计细则

2.1、K7 FPGA功耗评估

KINTEX-7 FPGA电源有数字电源VCCINT, VCCBRAM, VCCAUX, VCCAUX_IO ,VCCO和模拟电源VMGTAVCC ,VMGTAVTT, VMGTVCCAUX。

2.1.1、K7数字电源及时序(参考实战S1-FPGA板级实战导学)

Kintex7 FPGA系统数字电源电压大小:

VCCINT为FPGA内核供电引脚,需接1.0V;

VCCBRAM,为FPGA Block RAM的供电引脚;接1.0V;

VCCAUX为FPGA辅助供电引脚, 接1.8V;

VCCAUX_IO(IO辅助电压。推荐工作电压为1.8V/2V);

VCCO为FPGA的各个BANK的电压,包含BANK0,BANK12~18, BANK32~34;

2.1.2、K7模拟电源及时序

Kintex7 FPGA系统模拟电源电压大小:

VMGTAVCC为GTP收发器的供电电压,接1.0V;

VMGTAVTT为GTP收发器的端接电压,接1.2V;

MGTAVCCAUX为GTP收发器的供电电压的辅助电压,接1.8V;

2.1.3、K7 FPGA功耗评估(XPE)

《7_Series_XPE_2019_1_2》 excel算法

2.2、其余元器件功耗评估

2.2.1、DDR3 - MT41J256M16

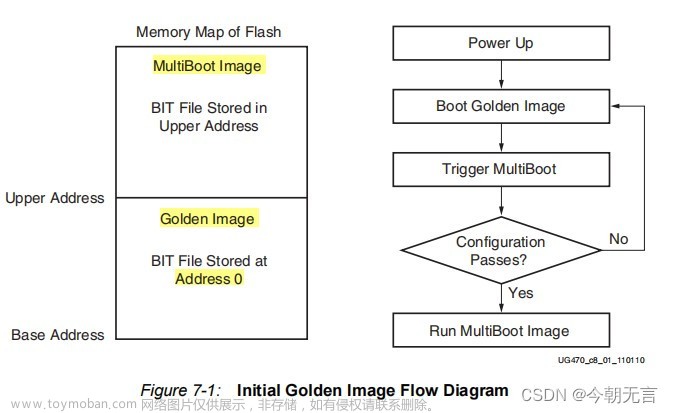

2.2.2、Spi flash -N25Q128

2.2.3、时钟差分-SIT9102

2.2.4、时钟buffer -SI5338

2.2.5、SODIMM内存条接口

2.2.6、USB转串口-CP2102

2.2.7、温度传感器-LM75

2.2.8、SFP光纤接口

2.2.9、QSFP+光纤接口

2.2.10、pcie金手指

2.2.11、SD卡槽

2.2.12、LED灯

2.2.13、FMC连接器

2.2.14、风扇

2.3.15、40针扩展接口(注意电平匹配)

2.3、各电源功能分配明细表

| 电源 |

功能 |

电流 |

| +12V |

风扇 |

|

| +1.0V |

FPGA 的内核电压 |

|

| +3.3V |

FPGA Bank0,Bank14,Bank15,QSIP FLASH, Clock 晶振, SD卡,SFP光模块 |

|

| +1.8V |

FPGA 辅助电压 |

|

| +1.5V |

DDR3, SODIMM,FPGA Bank33,Bank34,Bank35 |

|

| VADJ(+2.5V) |

FPGA Bank12, Bank13, FMC |

|

| MGTAVCC(+1.0V) |

FPGA Bank115, Bank116, Bank117,Bank118 |

|

| MGTAVTT(+1.2V) |

FPGA Bank115, Bank116, Bank117,Bank118 |

|

| MGT_1.8V (+1.8V) |

FPGA GTX 辅助电压 |

|

| DDR-VTT & VREF |

DDR和DIMM条的端接和参考电压 |

2.4、板级总功耗评估表(excel)

SUMPRODUCT函数

SUMPRODUCT函数是在给定的几组数组中,将数组间对应的元素相乘,并返回乘积之和。语法形式为SUMPRODUCT([array1], [array2], [array3], ...)。

2.5、电源时序图 (★)

文章来源:https://www.toymoban.com/news/detail-844917.html

文章来源:https://www.toymoban.com/news/detail-844917.html

2.6、电源树 (★)

2.7、电源参考总方案

文章来源地址https://www.toymoban.com/news/detail-844917.html

文章来源地址https://www.toymoban.com/news/detail-844917.html

3、K7板级电源设计注意事项(★)

3.1、各电源电压对应的电流及时序

3.2、FPGA电容取值

4、基于K7 板级的电源实战

4.1、电源入口

4.2、电源方案

4.3、电源实战图

详细内容参考视频讲解

到了这里,关于S5---FPGA-K7板级电源硬件实战的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!