CPU更适合处理复杂逻辑运算和单线程任务,而GPU则更适合处理大规模并行计算任务。

CPU(中央处理器)通常具有较少的核心数量(一般在2到16个之间),但每个核心的性能较强,擅长执行复杂的运算和逻辑任务,如浮点计算和整数计算。CPU在单线程任务上的性能通常较好,因为它们具有较大的缓存和较高的时钟频率。

GPU(图形处理器)拥有成百上千个小型处理核心,非常适合于处理大规模数据和执行高度并行的任务,例如图形渲染、深度学习和科学计算。虽然每个核心的计算能力相对较弱,但总体上GPU的计算能力非常强大,特别是在图像处理、模拟和计算密集型任务上。

CPU擅长控制单元和存储单元,逻辑运算单元,GPU擅长并行数学计算,做单精度或双精度浮点运算

CPU能力强数量少,GPU能力小数量多

独立显卡:GPU和显存、风扇,接口组成

架构区别:

CPU和GPU都是运算的处理器,在架构组成上都包括3个部分:运算单元ALU、控制单元Control和缓存单元Cache。

但是,三者的组成比例却相差很大。

在CPU中缓存单元大概占50%,控制单元25%,运算单元25%;

在GPU中缓存单元大概占5%,控制单元5%,运算单元90%。

GPU核心参数:

- 核心频率:频率越高,性能越强、功耗也越高。

- 显示位宽:单位是bit,位宽决定了显卡同时可以处理的数据量,越大越好。

- 显存容量:显存容量越大,代表能缓存的数据就越多。

- 显存频率:单位是MHz或bps,显存频率越高,图形数据传输速度就越快。

- CUDA Core:CUDA Core 是 NVIDIA GPU 上的计算核心单元,用于执行通用的并行计算任务,是最常看到的核心类型。NVIDIA 通常用最小的运算单元表示自己的运算能力,CUDA Core 指的是一个执行基础运算的处理元件,我们所说的 CUDA Core 数量,通常对应的是 FP32 计算单元的数量。

- Tensor Core:Tensor Core 是 NVIDIA Volta 架构及其后续架构(如 Ampere 架构)中引入的一种特殊计算单元。它们专门用于深度学习任务中的张量计算,如[矩阵乘法]和卷积运算。Tensor Core 核心特别大,通常与深度学习框架(如 TensorFlow 和 PyTorch)相结合使用,它可以把整个矩阵都载入寄存器中批量运算,实现十几倍的效率提升。

英伟达系列显卡大解析B100、H200、L40S、A100、A800、H100、H800、V100如何选择,含架构技术和性能对比带你解决疑惑

流处理器可以认为是一个独立的任务处理单元,也可以认为一颗GPU包含了数万个个CPU同时处理任务。

流处理器(SP,也可以把它称为Core),拥有的流处理器数量很多都是以千为基础单位的,有些甚至已经破万.

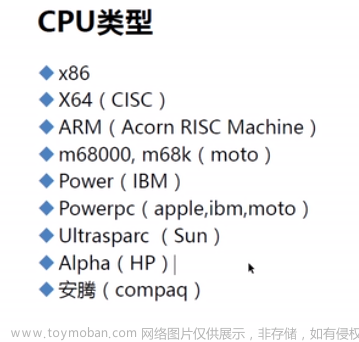

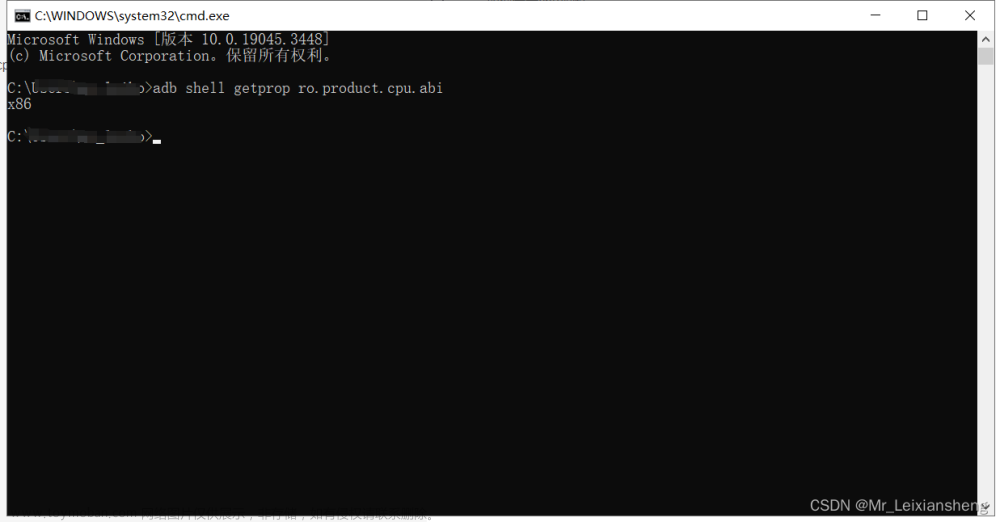

x86 arm risc-v cpu指令集

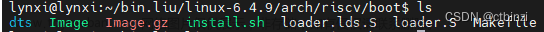

RISC-V已经成为继x86、ARM之后冉冉升起的第三大CPU架构

x86和arm都需要各自的公司intel ,ARM授权,而RISC-v开源

x86架构作为复杂指令集,一直统治PC电脑、HP高性能计算平台。

ARM属于精简指令级架构,用于大多数智能手机、嵌入式和物联网设备,低功耗和高性能。

RISC-V也是精简指令集,但开源开放免费,正逐渐成为不可忽视的重要力量,得到各个国家、企业的高度重视,我国很多自主芯片都是基于RISC-V架构。

intel,AMD,ARM三家公司在PC端一般采用x86复杂指令集,移动端一般采用arm指令集

cpu主频 是每秒发送的时钟脉冲数

CPU时钟周期 :一个是时钟脉冲所需要的时间,也叫节拍脉冲或T周期,它是CPU中最小的时间单位。

在流水线中一条指令的生命周期分为:

取指:

指令取指(Instruction Fetch)是指将指令从存储器中读取出来的过程。

译码:

指令译码(Instruction Decode)是指将存储器中取出的指令进行翻译的过程。经过译码之后得到指令需要的操作数寄存器索引,可以使用此索引从通用寄存器组(Register File)中将操作数读出。

执行:

指令译码之后所需要进行的计算类型都已得知,并且已经从通用寄存器组中读取出了所需的操作数,那么接下来便进行指令执行(Instruction Execute)。指令执行是指对指令进行真正运算的过程。譬如,如果指令是一条加法运算指令,则对操作数进行加法操作;如果是减法运算指令,则进行减法操作。在“执行”阶段的最常见部件为算术逻辑部件运算器(Arithmetic Logical Unit,ALU),作为实施具体运算的硬件功能单元。

访存:

存储器访问指令往往是指令集中最重要的指令类型之一,访存(Memory Access)是指存储器访问指令将数据从存储器中读出,或者写入存储器的过程。

写回:

写回(Write-Back)是指将指令执行的结果写回通用寄存器组的过程。如果是普通运算指令,该结果值来自于“执行”阶段计算的结果;如果是存储器读指令,该结果来自于“访存”阶段从存储器中读取出来的数据。

Superscalar Engines和VLIW(Very Long Instruction Word)是现代CPU设计中两种常见的指令级并行处理技术。在Superscalar Engines中,CPU通过同时发射多个指令来提高执行效率。这些指令可以相互独立,从而可以通过乱序执行和动态调度来充分利用处理器资源。VLIW则使用一个长指令字(Very Long Instruction Word)包含多个指令,并且这些指令共享一个执行单元和总线,从而实现高吞吐量的指令流水线。

这两种技术都依赖于处理器能够在单个时钟周期内执行多个指令,并且需要具有复杂的硬件结构来支持指令突发执行。因此,他们通常更适合用于执行大量并行任务的应用程序,例如多媒体处理或科学计算。

现代大多数CPU都是超标量的,即它们可以在同一周期内发射多于一个指令。发射宽度(Issue-width)是在同一周期内可以发射的最大指令数。当前一代CPU的典型发射宽度范围为2-6。为了确保正确的平衡,这种超标量引擎还支持多个执行单元和/或流水线执行单元。CPU还将超标量性能与深度流水线和乱序执行相结合,以提取给定软件的最大指令级并行性(Instruction-Level Parallelism)。

图9展示了一款支持2个宽度的超标量CPU的示例,即在每个流水线阶段处理两条指令。超标量CPU通常支持多个独立的执行单元,以避免冲突并保持流水线中的指令流动性。

CUDA全称(Compute Unified Device Architecture)统一计算架构,是NVIDIA推出的并行计算平台,它提供了相关API让开发者可以使用GPU完成通用计算加速(GPGPU),而不仅仅是图形计算

CUDA编程让你可以在CPU-GPU的异构计算系统上高效执行应用程序,语法只是在C语言的基础上做了简单的扩展,在开始编程前,我们首先得理清Host和Device的概念

- Host:CPU及其内存

- Device:GPU及其内存

运行在GPU设备上的代码我们称为kernel

典型的CUDA程序处理流程:

- 分配内存,数据初始化

- 将数据从Host拷贝到Device

- 调用kernels处理数据,然后存在GPU内存(Device)

- 将数据从Device拷贝到Host

- 内存释放

CUDA编程概述 - 知乎

nvcc是CUDA编译器:编译主机侧代码可以配置为gcc或clang,默认使用标准路径第一个编译器,设备层使用LLVM编译器进行编译。

nvcc --host-compiler=gcc/clang

CUDA(Compute Unified Device Architecture)是由NVIDIA推出的通用并行计算架构,它允许GPU解决复杂的计算问题。CUDA编程模型包括以下几个基本概念:

-

核函数(Kernel):在CUDA中,核函数是在GPU上执行的并行函数。每个线程执行相同的计算任务,但处理不同的数据。

-

线程(Thread):线程是CUDA编程的基本执行单位,每个线程都是一个独立的计算单元。

-

线程块(Thread Block):线程块是一组并行执行的线程,它们共享同一个代码和数据空间。线程块内的线程可以通过共享内存和同步机制进行通信和协作。

-

网格(Grid):网格是一组线程块,它们共享相同的核函数和执行配置。网格有助于将计算任务划分为更大、更易于管理的单位。

CUDA编程模型还引入了主机端和设备端的概念,其中CPU是主机端,而GPU是设备端。主机端负责复杂逻辑处理和运算量少的计算,而GPU则负责运行简单但计算量大的并行计算。

在CUDA编程中,线程组织结构可以是一维、二维或三维的。一维和二维组织结构分别将线程和线程块组织为线性数组和二维矩阵,适合处理不同类型的数据。

CUDA已经成为GPU计算的事实标准

cuda矩阵乘法:

矩阵规模

矩阵A: n行,l列

矩阵B:l行,m列

结果矩阵C=A✖️B: n行,m列

cuda矩阵乘法(简单理解)_cuda 矩阵乘法-CSDN博客

深入了解CUDA编程模型:并行计算的强大工具-CSDN博客 文章来源:https://www.toymoban.com/news/detail-845285.html

CUDA 编程指北:从入门到实践 - 知乎文章来源地址https://www.toymoban.com/news/detail-845285.html

到了这里,关于GPU-CPU-ARM-X86-RISC-CUDA的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!