Imagination APXM-6200 CPU:适用于智能、消费和工业应用的性能密集型RISC-V应用处理器

中国·上海 - 2024 年 4 月 8 日 - Imagination Technologies于今日推出Catapult CPU IP系列的最新产品 Imagination APXM-6200 CPU。这款RISC-V应用处理器具有极高的性能密度、无缝安全性和人工智能(AI)功能,可满足下一代消费和工业设备对计算和智能用户界面的需求。

SHD Group首席分析师Rich Wawrzyniak表示:“采用RISC-V架构的设备数量正在激增,预计到 2030年将超过160亿,而消费市场是推动这一增长的主要力量。到21世纪20年代末,每五台消费电子设备中就将有一台搭载RISC-V架构的CPU。Imagination正通过强调质量和简化采用过程的战略,确立其在RISC-V行业的影响力。APXM-6200 等产品将帮助RISC-V取得预期的成功。”

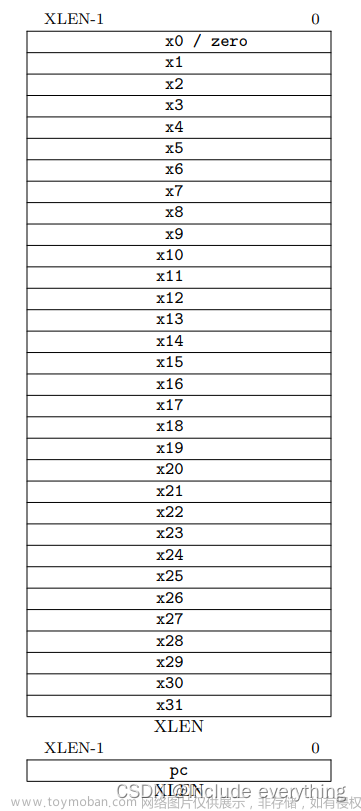

APXM-6200 CPU 是一款64位按序应用处理器,其双发11级指令流水线可为消费和工业工作负载提供同类产品中最佳的性能密度。客户可根据自己的性能需求选择单核、双核和四核配置,并可通过每核功率控制实现最高系统效率和缓存连贯性。由于支持RISC-V矢量扩展并具有专门针对AI加速器的快速数据耦合,这款处理器能够为AI功能提供助力。

Imagination Technologies计算副总裁Shreyas Derashri表示:“Imagination 为希望从采用 RISC-V架构的设计中获益的企业消除了障碍。我们正在大力投资于这个开源软件生态系统,以便在APXM-6200硅片上市时有可用的高性能软件堆栈。在硬件方面,我们的工程团队遵循严格的设计和验证流程。这一流程依靠 Imagination 三十年的复杂半导体 IP设计与支持经验日臻完善,可保证Catapult CPU达到最高的质量并以客户满意为宗旨。”

RISC-V International 首席执行官Calista Redmond 表示:“Imagination 在 RISC-V 社区和整个行业中都表现出了领导力,致力于将引人注目的创新产品推向市场。” Imagination公司在RISC-V领域的战略投资是RISC-V通过一套模块化标准规范和专有差异化技术所提供的独特设计潜力的绝佳例证。

轻松的设计迁移和灵活的用途

Imagination RISC-V解决方案中的Catapult SDK(软件开发套件)提供嵌入式开发人员为目标应用编写、构建和调试软件所需要的一切工具,包括一套能够提升AI工作负载性能的全新矢量计算库。除了 该SDK之外,Imagination还为微软流行的Visual Studio Code 集成开发环境(IDE)提供了一个名为Catapult Studio的扩展。现在,任何Visual Studio用户都可以访问该市场,并将该Catapult 扩展安装到他们的常规开发环境中。开发人员现在就可以抢在硬件上市之前,使用其中所包含的 QEMU(快速仿真器)和 Catapult 软件模型来构建和运行 RISC-V 软件。

在当今这个AI加持的互联世界中,安全性对于消费和工业应用至关重要。伴随着 RISC-V 的普及,向成熟安全框架无缝迁移势在必行。APXM-6200采用可与知名成熟安全框架无缝集成的多域隔离解决方案,能够在不影响安全性的情况下轻松导入到SoC设计中。

APXM-6200支持Android 和 Linux,预计将被用于智能电视、智能家居中枢和数字标牌等设备,其中许多设备还需要使用GPU处理图形用户界面。作为业界RISC-V架构 SoC的首选 GPU IP 供应商,Imagination 在设计 CPU、GPU 系统以提供更高性能方面具有独特的能力。当 APXM-6200 与 Imagination GPU 搭配使用时,总线利用率提高了一倍,内存流量减少了一半。此外,我们还与Lauterbach和 ProvenRun 等值得信赖的行业领军企业合作,一同加快我们客户的产品上市进程,确保他们能够以更低的成本实现及时部署。

ProvenRun首席执行官Thierry Chesnais表示:“安全性是电子行业最关心的问题。随着芯片复杂性和成本的增加,设计人员需要能够在不增加不必要的风险并且不重新设计安全架构的前提下,找到最适合其用例的IP。ProvenRun正与Imagination合作开发支持APXM-6200的ProvenCore TEE,使其安全套件达到行业标准并得到我们产品和服务的支持。”

Lauterbach GmbH首席技术官兼董事总经理Stephan Lauterbach表示:“工具市场已准备好支持想要使用RISC-V IP进行开发的企业。比如设计人员可以使用我们的Lauterbach TRACE32®工具集调试和控制任何 SoC 中的任何 RISC-V核,包括 Imagination的Catapult系列。我们今天宣布与 Imagination建立合作伙伴关系不仅是为了支持 APXM-6200,也是为了共同推动 RISC-V取得更大的成功。此举意在告诉企业可以放心地投资 RISC-V 产品,因为他们知道自己的产品可以快速推向市场并达到客户期望的质量水平。”

更多信息,请在4月9日至11日期间参观Imagination Technologies在Embedded World上的展台(4号展厅4-659展位)或在 https://www.imaginationtech.com 订阅有关Imagination Catapult CPU系列产品的信息。文章来源:https://www.toymoban.com/news/detail-845323.html

关于Imagination Technologies

Imagination是一家总部位于英国的公司,致力于打造半导体和软件知识产权(IP),使客户在竞争激烈的全球技术市场中获得足够优势。公司的图形处理器(GPU)、中央处理器(CPU)和人工智能(AI)技术可以实现出众的PPA(功耗、性能和面积)指标、快速的上市时间和更低的总体拥有成本(TCO)。基于Imagination IP的产品被全球数十亿人用于他们的手机、汽车、住宅和工作场所。请访问https://www.imaginationtech.com/。文章来源地址https://www.toymoban.com/news/detail-845323.html

到了这里,关于Imagination 推出全新Catapult CPU,加速RISC-V 设备采用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!