此系列记录FPGA在学校的学习过程。

FPGA系列

需要用到的软硬件:

软件:Quartus II 15.0 (64-bit)

硬件:

5CEBA4F23C7芯片

1.创建新的工程在下面链接

链接:

FPGA在校学习记录系列—新建一个FPGA工程编写程序并仿真(Verilog HDL)

创建的工程名字为:LED

2.创建好工程后添加代码

(这次不用仿真,直接用开发板验证)

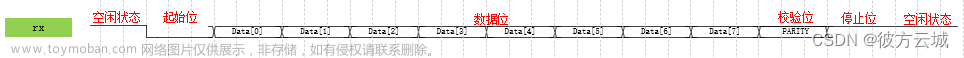

module LED(clk,rst,in,out);

input clk,rst,in; // clk M9时钟,rst拨码开关低电平复位,in拨码开关控制

output reg [9:0] out;

always @(posedge clk or negedge rst)

begin

if(!rst)

out = 10'b 0000000000 ;

else if (in)

out = 10'b 1010101010 ;

else

out = 10'b 0101010101 ;

end

endmodule

编译文件

3.设置锁定管脚

首先查阅开发板上的资源

按键资源:

LED资源:

拨码开关:

打开软件后,打开引脚设置

使用了全部的LED

sw0开关用于复位

sw1开关用于切换状态

将它们的管脚对应上芯片

设置好后关闭,再次点击编译

4.安装驱动

在安装路径drivers下,双击.exe文件

驱动前两个安装失败是正常的

5.将程序下载进开发板中

(下载前要编译成功)

打开烧录下载界面

先将开发板与电脑连接好

选择下载端口

(使用数据线连接电脑才能选择端口)

选择烧录文件

点击start开始下载程序

下载好程序后右上角会显示下载成功

6.开始验证

SW0=0时,为复位状态,所有灯都不亮文章来源:https://www.toymoban.com/news/detail-845823.html

SW0=1时,亮灯为1010101010(从右往左,因为LED0在最右边)

SW1=1时,亮灯为0101010101(从右往左,因为LED0在最右边) 文章来源地址https://www.toymoban.com/news/detail-845823.html

文章来源地址https://www.toymoban.com/news/detail-845823.html

到了这里,关于FPGA在校学习记录系列---实验4不同状态的LED+开发板(Verilog HDL)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!