目录

一 前言

Vivado 版本

Vivado 2018.03

芯片

ZYNQ-XC7Z010

VSCode

安装最新版本就行

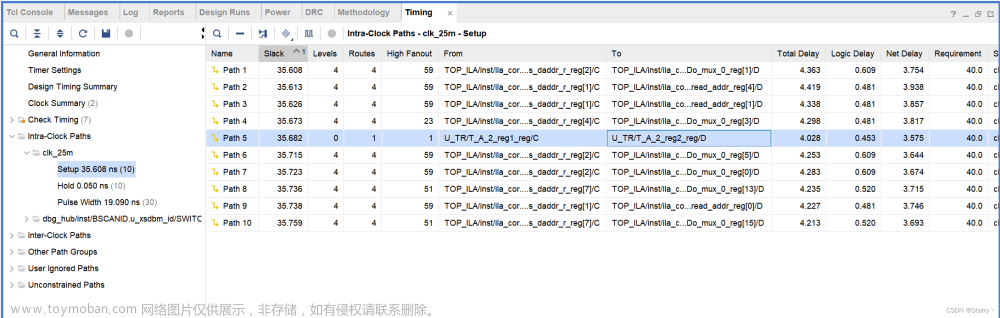

二 Vivado 设置编译方式

Tools

Text Editor

设置 VSCode 地址

编辑三 VSCode 插件安装

1. Verilog HDL/SystemVerilog

打开vscode,打开拓展界面

环境变量设置

2. SystemVerilog

编辑 设置为默认缩进软件(如图所示)

3. Verilog HDL

🫡欢迎进行技术讨论🫡

一 前言

最近开始学习FPGA的开发,下面就我个人学习的一个阶段做一个总结与记录,以及分享我所找到的一些资料给大家做个参照~~文中有不足之处望指教。

这个文章主要包含了 Vivado 的安装 以及如何使用 VSCode 进行代码部分的编写,当然也有很多其他的编辑器可以使用,开发的平台选择好了我们也可以事半功倍~~

我是因为我开发STM32的时候就是使用 VSCode 编辑器进行开发的,就难得去下载其他编辑器了

Vivado 版本

Vivado 2018.03

给大家附上安装包连接等,安装教程我就不一一叙述了,直接放到网盘中

主要安装不要有中文就行啦!

Vivadohttps://pan.baidu.com/s/1EU-_VPD-O8kaTjkv7DYLZg?pwd=xzy0%C2%A0

芯片

ZYNQ-XC7Z010

Zynq-7000 系列芯片是基于Xilinx 的可扩展处理器平台架构(Extensible

Processing Platform, EPP),将双核ARM Cortex-A9 处理器和FPGA 可编程逻辑单

元集成在一颗单芯片中,从而构成了PS(Processing System)加PL(Programmable

Logic)的单芯片SoC 解决方案。初学来讲,这款芯片性价比较高,也有完善的学习资料

VSCode

安装最新版本就行

VSCode官网https://code.visualstudio.com

二 Vivado 设置编译方式

Tools

点击 Tools 的 Setting 功能

Text Editor

点击 Text Editor 中的 最后一个选项

设置 VSCode 地址

将我们安装的 VSCode 编辑器地址复制放入 Editor 中

红色字为需要修改的部分 修改后将尾部文字复制粘贴即可

D:\Program\VSCode\Microsoft VS Code\Code.exe -g [file name]:[line number]

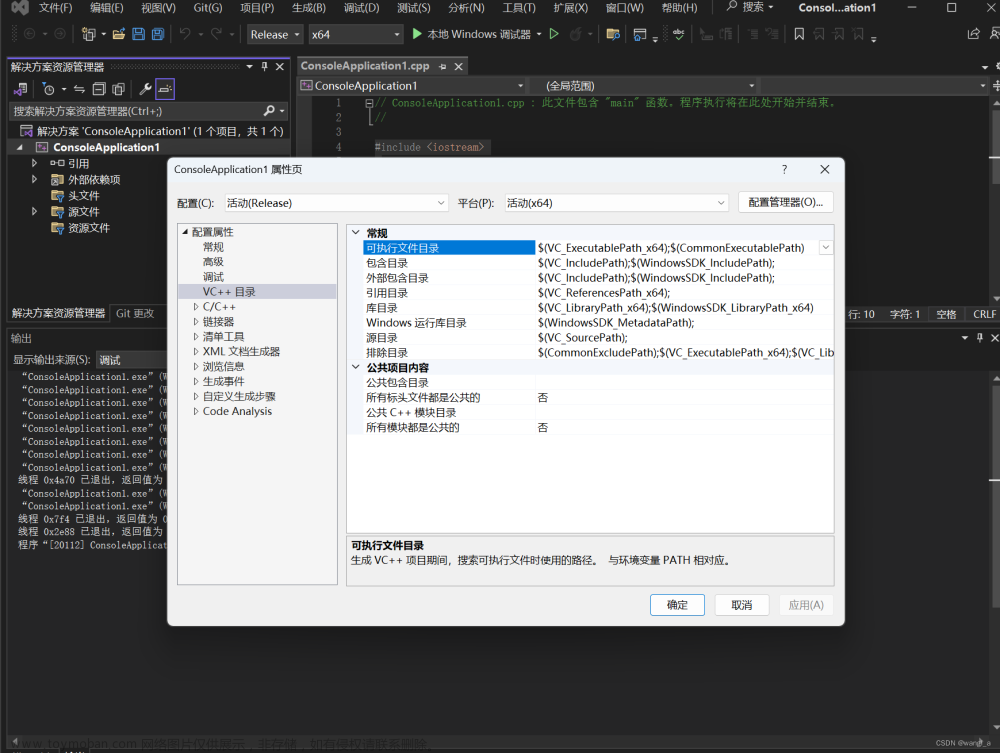

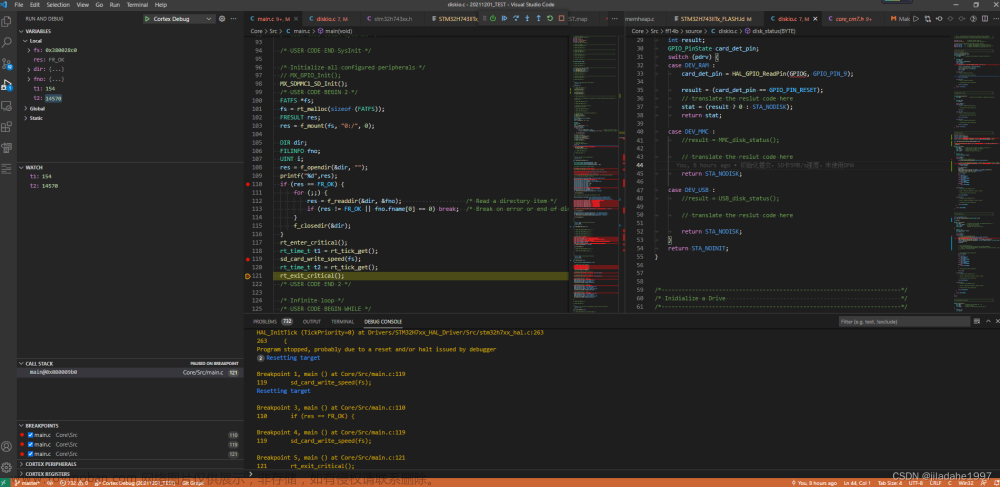

三 VSCode 插件安装

1. Verilog HDL/SystemVerilog

是实现语法高亮,自动补全、列出端口等,直接在vscode 插件库中,搜索 Verilog HDL/SystemVerilog 下载即可。

打开vscode,打开拓展界面

环境变量设置

2. SystemVerilog

语法自动缩进

设置为默认缩进软件(如图所示)

设置为默认缩进软件(如图所示)

3. Verilog HDL

文章来源:https://www.toymoban.com/news/detail-846355.html

文章来源:https://www.toymoban.com/news/detail-846355.html

🫡欢迎进行技术讨论🫡

⚠️⚠️END⚠️⚠️文章来源地址https://www.toymoban.com/news/detail-846355.html

到了这里,关于FPGA开发 -- Vivado使用VSCode编译带图文(安装 语法校验 自动缩进 )的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!