1.集成12位DAC和ADC的一款器件,2个输入模拟通道和2个输出模拟通道

2.• TX频段:47 MHz至6.0 GHz • RX频段:70 MHz至6.0 GHz

3.SPI配置成LVDS或CMOS接口,也可以还可以选择FDD(频分双工——全双工,操作时需要两个独立的信道)或TDD(时分双工——半双工,只需要一个信道)工作方式

4.由于9361的寄存器较多,首先利用AD936X Evaluation Software 软件(安装包在百度网盘里面),根据我们的项目需求,配置相应的功能参数,生成寄存器参数配置文件。详细配置流程

csdn - 安全中心

5.好像也有官方代码——尤老师在B站有相关视频讲解

6.设置ENSM,强烈建议,不管你项目使用的是FDD或者TDD的工作方式,均建议采用FDD模式,在FDD独立模式下,通过控制ENABLE和TXNRX两个引脚,也可以实现TDD的收发单独控制。

7.点击OK生成配置文件。但是配置文件不能直接在工程中使用,需要将其转化成Verilog格式,下一章介绍我自己编写的脚本转化软件,可直接将配置脚本生成Verilog的function函数,方面工程直接调用。

8.实际运用中出现配置完后切换另一个频点出现频偏的问题

参考人家的解决办法——如果需要快速跳频工作,那还需要加入Profile的校准相关的代码

AD9361纯逻辑控制从0到1连载5-fast lock的简介-CSDN博客

AD9361纯逻辑控制从0到1连载6-fast lock之profile寄存器设置_ad9361 fastlock-CSDN博客

AD9361纯逻辑控制从0到1连载7-根据射频频率计算VCO参数_ad9361 rfvco不锁定-CSDN博客

9:

REFCLK Path——

XTALP/XTALN:参考频率 REF_CLK晶振连接。使用晶振时,将其连接于这两个引脚之间。使用外部时钟源时,将其连接至XTALN,使XTALP保持断开。

第一个选择是使用一个专门的晶振,其频率在19 MHz和50MHz之前,连接于XTALP和XTALN引脚之间。

第二个选择是将一个外部振荡器或时钟分配器件(如AD9548)连接至XTALN引脚(其中, XTALP引脚保持断开状态)。如果使用外部振荡器,则频率可在10 MHz和80 MHz之间变化。

10.由于BPLL的时钟频率范围是(700M-1400M),BB PLL频率合成器,用于生成所有与基带相关的时钟信号包括ADC和DAC采样时钟

11.由于BBPLL 参考时钟频率最好在35-70MHz中选大的值,RF PLL 参考时钟频率最好在10-80MHz中选大的值,所以BBPLL和RFPLL 分别为1x和2x————这个地方不理解

12.DCXO Options:如果参考时钟是外部输入时钟,忽略该项。如果参考时钟为DCXO,由于DCXO可以通过coarse word和 fine word,调整产生的DCXO频率,需要根据设备实际情况设置该项,目前先使用默认值。

13.

AD9361包含8个profile,每个profile包含16个8位寄存器,后面称为REG0~REG15。其中REG0 ~ REG4是根据射频频率计算出来的,REG6 ~ REG13是根据VCO的频率查表查到的,这个表是一个文件集,包含SynthLUT_40_TDD.txt,SynthLUT_40_FDD.txt,SynthLUT_60_TDD.txt,SynthLUT_60_FDD.txt等,根据实际情况选择使用哪个表。如果你已经安装了前面章节提到的脚本生成软件,则可以在路径 …/AD9361R2 Evaluation Software 2.1\data\下面找到这些表。

只工作 在8个频点上,那恭喜你,可以省不少事。因为ad9361自带8个profile,所以在系统跑起来之前,你可以校准好8个频点,每个profile存储一个,后面直接调用其中某个profile,系统就切换到对应的频率了。文章来源:https://www.toymoban.com/news/detail-846445.html

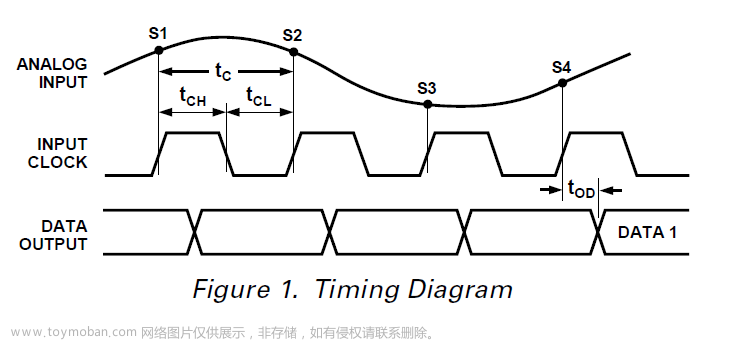

14.spi命令分为两个阶段,阶段1是传输都还是写+寄存器地址,阶段2才是传输的具体指令文章来源地址https://www.toymoban.com/news/detail-846445.html

到了这里,关于FPGA_AD9361的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!