一、什么是FPGA,内部资源构成?

答:FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可以通过编程来配置的半导体设备。FPGA由成千上万个可配置逻辑块(CLB)和可编程的互联资源组成,可以实现复杂的数字计算功能。与其他类型的集成电路相比,如专用集成电路(ASIC)或标准逻辑IC,FPGA的独特之处在于其可编程性,允许设计者在不需要改变硬件本身的情况下,通过改变内部配置来改变其功能。(灵活、并行处理、功耗高、成本高)

FPGA的内部资源可以分为几个主要部分:

1. 可配置逻辑块(CLBs)或逻辑元件(LEs)

定义:CLBs是FPGA的基本构建块,负责实现逻辑功能。每个CLB可以包含若干个逻辑元件(LEs),这些逻辑元件包含查找表(LUTs)、触发器(如D触发器),以及逻辑运算单元等。

功能:通过编程配置,CLBs可以实现从简单的逻辑门(如AND、OR、NOT)到更复杂的组合逻辑和时序逻辑电路。

2. 查找表(LUTs)

定义:LUT是FPGA中实现逻辑功能的关键组件,它是一种可编程的存储器,用于存储逻辑函数的真值表。

功能:通过配置LUT,可以实现任何逻辑函数,这使得FPGA能够执行复杂的逻辑运算。

3. 可编程互联资源

定义:FPGA中的可编程互联资源包括一系列的编程开关和连接矩阵,用于连接CLBs、I/O块、和其他资源。

功能:这些资源确保了FPGA内部的不同部分可以灵活地连接在一起,以构建复杂的数字电路。

4. 输入/输出块(IOBs)

定义:IOBs是FPGA与外部世界连接的接口,位于FPGA芯片的边缘。

功能:IOBs提供了多种标准和专用的接口,如LVDS、PCIe、Ethernet等,以支持与外部设备的数据通信。

5. 嵌入式多用途块

存储器块(如BRAM - Block RAM):提供大量的内部存储,可用于实现FIFOs、缓存、或其他临时存储需求。

数字信号处理块DSP slices):专为执行加法、乘法、累加等高性能数字信号处理操作而设计。

时钟管理模块(如PLLs和MMCMs):提供时钟生成、分频、倍频、时钟选择等功能,对于实现复杂的时钟体系至关重要。

6. 高速串行接口

定义:某些FPGA提供高速串行接口,如SerDes(串行化/反串行化器),用于支持高速数据传输。

功能:这些接口常用于实现高速通信协议,如Gigabit Ethernet、PCI Express、Fiber Channel等。

二、同步/异步电路

1.同步时钟问题

同步时钟指的是设计中使用的时钟信号遵循一定的规则和策略,以确保信号在不同的时钟域之间正确地传输和处理,避免时钟偏差和时序问题。

重要性:

1. **稳定性**:同步时钟可以确保在整个设计中,所有的逻辑块和处理单元都能在正确的时间接收到时钟信号,这对于维护信号的完整性和防止数据损坏至关重要。

2. **性能**:通过优化时钟分配和管理,可以最大化FPGA的性能,提高数据处理速度和响应时间。

3. **时序一致性**:在设计中使用同步时钟有助于保持时序一致性,确保数据在预期的时钟周期内被正确地处理和传输。

实现同步时钟的方法:

1. **全局时钟网络**:FPGA通常提供全局时钟网络(GCLK),这是专为传输时钟信号而设计的高性能、低偏差的互联网络。利用全局时钟网络可以最小化时钟偏差,确保时钟信号在整个芯片范围内的一致性。

2. **时钟管理单元**:如PLL(相位锁环)和MMCM(混合模式时钟管理器)等时钟管理单元能够生成多个频率相同或不同的稳定时钟信号。这些单元能够对输入时钟进行倍频、分频、相位调整等操作,满足复杂设计中的时钟需求。

3. **时钟域交叉(CDC)处理**:在涉及多个时钟域的设计中,数据从一个时钟域传输到另一个时钟域时,需要采用CDC技术来确保数据的正确传输,避免因时钟差异引起的数据不稳定。常见的CDC方法包括使用双触发器同步法、FIFO缓冲等技术。

4. **静态时序分析(STA)**:设计阶段进行静态时序分析,可以预先发现和修正可能的时序问题,确保设计满足时序要求。STA工具能够分析在最坏情况下的数据路径,帮助设计者优化时钟设计。

(以后打算出几期深入探讨一下这些问题)

2.同步/异步电路

同步电路:同步电路是指所有的操作都是在一个共同的时钟信号的控制下进行的。这个时钟信号以固定频率产生脉冲,所有的逻辑操作都在时钟脉冲的触发下同步进行。

异步电路:异步电路不依赖于统一的时钟信号进行操作,而是通过事件的发生来触发操作,由于操作不依赖于统一的时钟信号,因此异步电路在某些情况下可以提供更高的灵活性和效率。

三、同步/异步复位

同步复位:

同步复位指的是复位信号在触发操作时受到时钟信号的控制,即复位操作仅在时钟边沿发生时才执行。这种方式下,复位信号被视为电路中的一个普通同步信号,需要经过触发器的同步过程。在时序分析中易于处理,因为所有操作包括复位都遵循相同的时钟边沿。由于复位信号的同步性,可以减少复位过程中产生亚稳态的风险。复位信号的响应需要等待下一个时钟边沿,可能导致复位响应不够及时。每个需要同步复位的触发器都必须设计额外的逻辑来处理复位逻辑,可能增加资源消耗。

异步复位:

是指复位信号可以在任何时间直接对电路产生影响,不需要等待时钟信号的边沿。这意味着一旦检测到复位条件,电路可以立即被复位。可以立即响应复位信号,不受时钟周期的限制,适合紧急停止或快速重新启动的场景。为设计提供了更多灵活性,可以在任何时刻迅速将电路恢复到安全或已知状态。由于复位发生在非时钟边沿,可能增加进入亚稳态的风险。需要额外的电路来确保复位解除(de-assertion)是同步的,以避免在复位解除时产生的亚稳态问题。

复位信号的解除:

无论是同步复位还是异步复位,在解除复位时,通常采用同步解除的方式。这意味着复位解除信号的变化会在时钟边沿同步到电路中,以减少亚稳态风险。

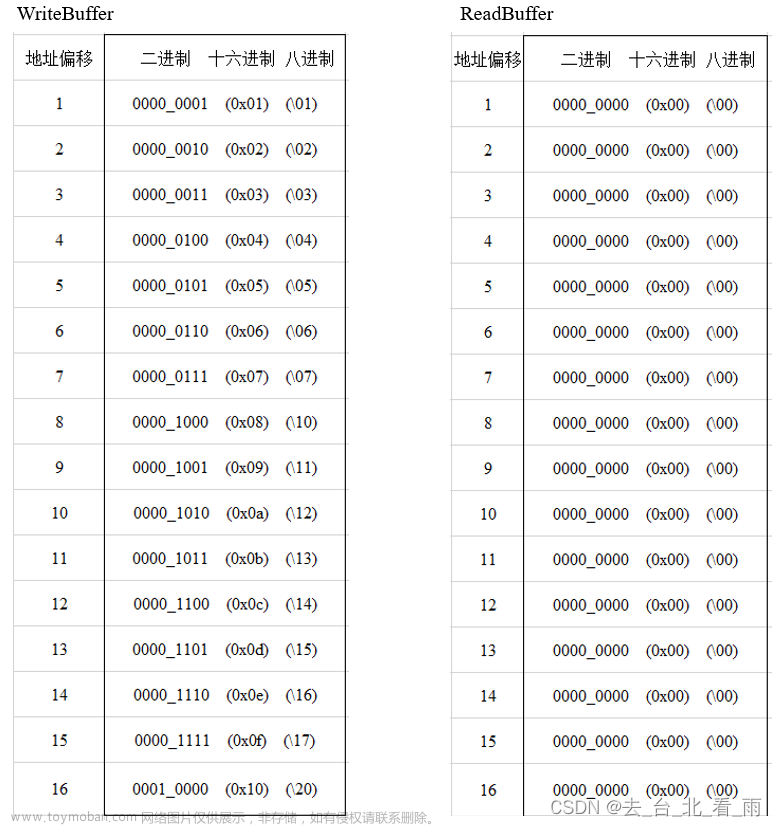

四、同步/异步fifo

FIFO(First-In, First-Out)队列是一种重要的数据结构,广泛应用于硬件设计和系统架构中,用于在不同的处理单元或不同的时钟域之间传递数据。根据数据同步的方式,FIFO可以分为同步FIFO和异步FIFO。

同步FIFO:

指的是写入端和读出端都使用同一个时钟信号。在这种FIFO中,数据的写入和读出操作都在同一个时钟域内完成,因此时钟同步问题相对较少,设计和实现相对简单。

异步FIFO:

异步FIFO允许写入端和读出端工作在不同的时钟域下,这种设计在处理生产者和消费者运行在不同频率或者需要跨越不同时钟域进行数据传输的场合非常有用。支持两个不同的时钟域,一边用于写入,另一边用于读出,适用于连接不同速率的模块。需要特别的设计来处理时钟域之间的交叉(CDC)问题,以确保数据的完整性和一致性。

在设计异步FIFO时,主要挑战是处理不同时钟域之间的数据一致性和完整性问题。为此,通常需要采用以下一些策略

指针同步:使用格雷码计数器(Gray code counter)来同步读写指针,因为灰码计数器在任何时刻只改变一位,这减少了在不同时钟域之间同步时的错误概率。

满和空状态检测:设计合理的满和空状态检测逻辑,确保在任何时钟域下,都能准确判断FIFO的状态,避免数据丢失或重复读取。

五、逻辑电平

逻辑电平是数字电路设计中的基础概念,用于表示信号的状态。不同的技术和标准可能定义了不同的逻辑电平范围,这些电平通常分为高电平(逻辑"1")和低电平(逻辑"0")。以下是一些常见的逻辑电平标准:

TTL(晶体管-晶体管逻辑)

高电平(逻辑"1"):一般在2.0V到5.0V之间。

低电平(逻辑"0"):一般在0V到0.8V之间。

CMOS(互补金属氧化物半导体)

高电平(逻辑"1"):通常接近VDD(供电电压),例如在5V供电系统中高电平接近5V,在3.3V系统中接近3.3V。

低电平(逻辑"0"):通常接近GND(地),几乎为0V。

LVCMOS(低电压CMOS)

高电平(逻辑"1")和**低电平**(逻辑"0"):与CMOS类似,但操作电压更低,如1.8V、2.5V或3.3V。

LVTTL(低电压TTL)

高电平(逻辑"1"):通常在2.0V到3.3V之间。

低电平(逻辑"0"):一般在0V到0.8V之间。

PECL(正发射极耦合逻辑)

高电平(逻辑"1"):通常比地电平高约3.3V。

低电平(逻辑"0"):比高电平低约0.8V到1.0V。

LVDS(低电压差分信号)

不是基于绝对电平,而是基于两个线之间电压的差异来表示逻辑状态。

高电平(逻辑"1"):差分电压正值,约为+350mV。

低电平(逻辑"0"):差分电压负值,约为-350mV。

RS-232

高电平(逻辑"1"):通常在-15V到-3V之间。

低电平(逻辑"0"):通常在+3V到+15V之间。

建立时间(Setup Time)和保持时间(Hold Time)是数字电路中,特别是在时钟同步系统中非常关键的概念。这些参数确保数据在触发器(如D触发器)中能够正确地被捕获和存储。

六、建立\保持时间

建立时间(Setup Time):

是指在触发器的时钟信号到来之前,数据信号必须保持稳定的最小时间。换句话说,数据必须在时钟信号的上升(或下降)边沿到来之前的一段时间内稳定,以确保数据能被触发器正确捕获。如果数据在这个时间窗口内发生变化,触发器可能会捕获错误的数据,导致未定义的行为。

保持时间(Hold Time):

保持时间是指在触发器的时钟信号到来之后,数据信号必须保持稳定的最小时间。这意味着数据必须在时钟信号的上升(或下降)边沿到来之后保持不变一段时间,以确保数据被正确地存储在触发器中。如果数据在保持时间内发生变化,同样可能导致触发器捕获错误的数据。

时钟偏斜(Clock Skew):

时钟信号在到达不同部件时可能会有延迟差异,这种差异可能会影响建立时间和保持时间的计算。设计时需考虑时钟偏斜,以确保系统的稳定性。

数据路径延迟:

数据从发送端到达触发器的时间也会影响是否能满足建立和保持时间的要求。设计高速数字电路时,对数据路径的分析非常关键。

七、"recovery time"和"removal time"

Recovery Time:

是指在某些数字电路或系统(特别是带有异步复位或使能信号的电路)中,从一个特殊控制信号(如复位或使能信号)被解除(即从激活状态回到非激活状态)到下一个有效操作(如时钟边沿)之间必须保持稳定的最短时间间隔。这个时间是为了确保电路从控制信号的影响中完全恢复,并准备好接受下一次操作。违反recovery time要求可能会导致电路行为不稳定或不可预测。

Removal Time:

Removal time通常与recovery time相关,但它是从另一个角度来定义的时间间隔。Removal time是指在触发器或其他电路元件的控制信号(如复位或使能)需要保持激活状态的最后一个有效操作(通常是时钟信号的一个边沿)之后,控制信号可以被安全移除(解除激活)的最短时间间隔。简而言之,它是控制信号在不影响电路当前操作的情况下可以被移除的最短时间。

Recovery time确保在控制信号解除后电路有足够的时间恢复到正常工作状态,准备接受下一次的正常操作。Removal time则确保在进行下一次正常操作之前控制信号被保持足够长的时间,以确保其产生的效果被完全实现。文章来源:https://www.toymoban.com/news/detail-847326.html

(未完待续)文章来源地址https://www.toymoban.com/news/detail-847326.html

到了这里,关于FPGA面试试题(附个人整理答案)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!