基于xilinx k7 325t实现的千兆网udp协议,只需要设置好IP,端口,就可以直接给数据,基本等同于透传,可以不用管底层协议。

可以

# FPGA 实现udp模块说明

## udp_protocol_top

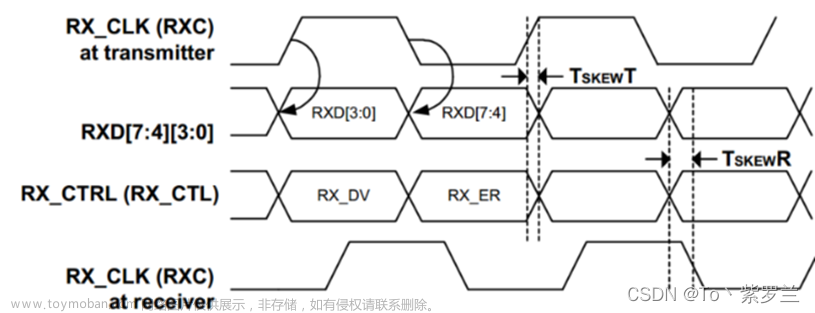

gig_ethernet_pcs_pma有脚本生成,任何版本vivado都可以支持,注释里面有对重要信号的说明,默认是1000M,100M需要改内部信号,PHY芯片是88E1512,SGMII接口。

FPGA和上位机IP,端口都要设置好才能收到数据,注意在同一个网段

## 接收数据

udp_protocol_top.rx_udp_payload_axis_tvalid拉高的时候就代表udp_protocol_top.rx_udp_payload_axis_tdata有效,udp_protocol_top.rx_udp_payload_axis_tready默认给1可以一直收数据

## 发送数据

tx_udp_payload_axis_tready=1的时候拉高tx_udp_payload_axis_tvalid,数据才有效,发送完成以后一定要发送一个tx_udp_payload_axis_tlast脉冲指示最后一个数据

基于Xilinx K7 325T实现的千兆网UDP协议

在计算机网络中,UDP(User Datagram Protocol)是一种无连接的、不可靠的传输协议。它通过将数据分为数据报,使用IP(Internet Protocol)进行传输,具有较低的延迟和较小的网络开销。本文将介绍基于Xilinx K7 325T实现的千兆网UDP协议,该实现采用FPGA作为硬件平台,可以通过设置IP和端口,直接传输数据。本文将详细讲解实现的原理和使用方法。

首先,我们使用Xilinx K7 325T作为FPGA硬件平台。该型号的FPGA具有丰富的资源和高性能,可以满足千兆网UDP协议的要求。在实现过程中,我们使用了gig_ethernet_pcs_pma模块作为物理层的实现。该模块可以通过脚本生成,支持任何版本的Vivado开发工具。在模块的注释中,有对重要信号的说明。默认情况下,该模块的传输速率为1000M,在需要使用100M速率时,需要修改内部信号。与FPGA相连的PHY芯片采用的是88E1512,接口采用SGMII。

在实现UDP协议时,首先需要设置FPGA和上位机的IP和端口。只有当IP和端口设置正确并且在同一个网段时,FPGA才能正确地接收数据。

接收数据的过程如下:当udp_protocol_top.rx_udp_payload_axis_tvalid信号拉高时,代表udp_protocol_top.rx_udp_payload_axis_tdata有效。而udp_protocol_top.rx_udp_payload_axis_tready信号默认为1,表示FPGA一直可以接收数据。

发送数据的过程如下:当tx_udp_payload_axis_tready信号为1时,拉高tx_udp_payload_axis_tvalid信号,表示数据有效。发送完最后一个数据后,一定要发送一个tx_udp_payload_axis_tlast脉冲,指示最后一个数据。

通过以上简单的设置,我们就能够基于Xilinx K7 325T实现千兆网UDP协议。这种实现方式简单高效,只需要设置IP和端口,即可实现数据的传输,无需关心底层协议。在使用过程中,需要注意确保FPGA和上位机的IP和端口设置正确,并且位于同一网段。

本文介绍了基于Xilinx K7 325T实现的千兆网UDP协议。通过该实现,我们可以方便地进行数据传输,无需关心底层协议的细节。该实现方式简单高效,适用于各种需要进行千兆网数据传输的应用场景。希望通过本文的介绍,能够对读者有所启发,提供一种简单而实用的技术解决方案。文章来源:https://www.toymoban.com/news/detail-847856.html

相关代码,程序地址:http://lanzoup.cn/665179393064.html

文章来源地址https://www.toymoban.com/news/detail-847856.html

到了这里,关于基于xilinx k7 325t实现的千兆网udp协议的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!