1. 电路知识

1.1. 驱动能力

IC是数字逻辑芯片,其输出的是逻辑电平。逻辑电平0表示输出电压低于阈值电压,逻辑1表示输出电压高于阈值电压。负载则是被驱动的电路或元件,负载大小则指负载的电阻大小。

驱动能力主要表现在几个方面:

-

负载能力:负载过大表现为外部负载的阻值过小,在电压不变的情况下,过小的阻值会导致电流过大,可能会烧坏器件。负载过小,表现为外部负载的阻值达大,在电压不变的情况下,过大的阻值会导致电流过小,信号会延迟和衰减。负载能力表现为其电流大小范围,所以外部负载大小必须合理设计。

-

扇出(Fan-out)能力:表现为可以驱动多少个外部端口。

-

响应速度:信号上长下降的时间,这也决定了信号工作频率的最大值。

1.2. 逻辑电平

逻辑电平是指在数字电路中表示逻辑状态(0或1)的电压或电位。它用于确定信号的“低”和“高”状态,以便进行逻辑运算和数据处理。

-

TTL(Transistor-Transistor Logic)电平:TTL是一种广泛使用的逻辑电平标准,TTL电路通常需要5伏特的供电电源,阈值电压通常为2V。

-

CMOS(Complementary Metal-Oxide-Semiconductor)是一种常见的逻辑电平标准,广泛应用于数字集成电路和数字系统中。CMOS电平使用的是互补的MOSFET(金属氧化物半导体场效应晶体管)来表示逻辑状态。CMOS的工作电压为5V、3.3V、1.8V、1.2V甚至更低。CMOS电平是现代IC的主流电平。CMOS电平的阈值电压一般为工作电压的一半。

1.3. 输出状态

I/O的引脚输出状态除了高低电平两种状态之外,还有一个高阻状态(意味着阻值非常大,极限是悬空无穷大)。高阻状态在集成电路也被叫做Z态,其电平可能高也可能低,是受外部电路影响的。高阻态是一种输入状态,用来接收外部输入信息。

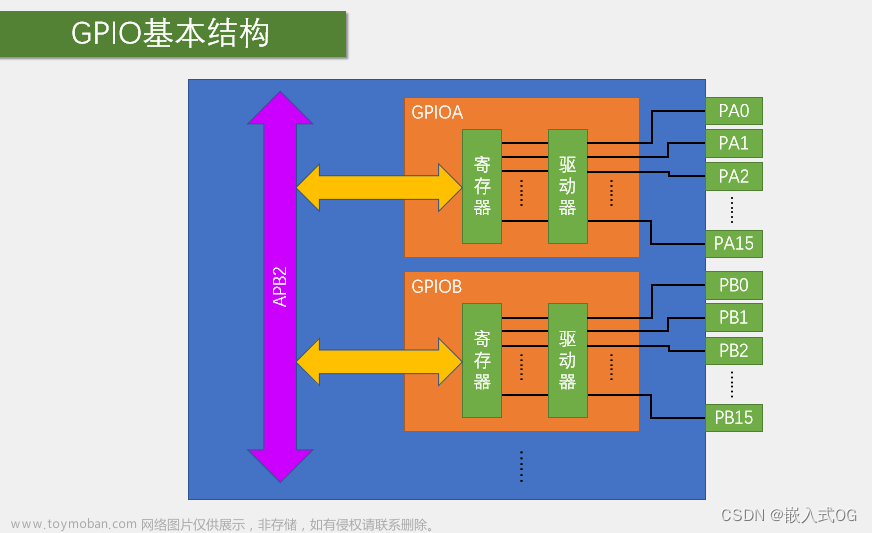

1.4. GPIO

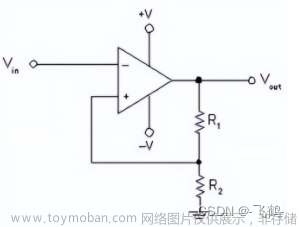

芯片内存的输入电路一般是使用施密特触发器实现的,其作用是当输入电平高于阈值电压时,其输出一个稳定的高电平,当输入电平低于阈值电压时,其输出一个稳定的低电平。下图不IC输入电路示意图:

GPIO(General-purpose input/output),通用目的输入输出,指示IC的Pin可以用作输出或输入使用。

1.4.1. 输入模式

IO的输入模式表示IO准备用来接收外部信号的输入,其有3种状态。

-

高阻(High resistance)状态,即IO引脚处于一种高阻值状态,此状态不稳定,易受外部影响导致变高变低,不推荐使用。

-

上拉电阻(Pull-up resistor),在输入模式下将引脚通过一个电阻与电源相连,这样就能够保证引脚在默认情况即位于高电平。上拉电阻(Pull-up resistor),在输入模式下将引脚通过一个电阻与电源相连,这样就能够保证引脚在默认情况即位于高电平。因为IC有内阻,接入适合大小的上拉电阻,可以让输入引脚处电压为3.3V。当外部输入低电平时,无论是否接上拉电阻,输入电平都为0。上拉电阻也会在开漏输出中使用,选择合适的上拉电阻,可以提供相应的高电平。如下图,IIC总线上的SLC/SDA接了上拉电阻,这是因为EEPROM的SCL/SDA要求空闲时为高电平。

-

下拉电阻(Pull-Down Resistor),在输入模式下,将引脚通过电阻连接到地,让引脚的高阻态变为低电平。

1.4.2. 输出模式

如下图,是一个IC输出引脚的内部电路示意图。通过控制2个MOS,理论上可以输出4种状态,但是Q1和Q2同时打开导通时,会造成短路异常。所以控制2个MOS管,可以输出3种有效状态。

-

推挽输出(Push-Pull Output):IO的驱动是通过电流来表现的,电流向往流,表现为推(Push),输出高电平。当电流往里流,表现为挽(Pull),输出低电平。推挽模式通过Q1打开Q2关闭、Q1关闭Q2打开来实现输出高电平和低电平。高电平和低电平组成推挽输出。

-

开漏输出(Open-Drain Output):假如IC的输出高电平为5V,而外设器件只支持3.3V。推挽输出的高电平可能导致外设器件烧坏,此时可以使用开漏输出。MOS管Q1关闭和Q2打开,此时可以正常输出低电平。MOS管Q1和Q2都关闭,此时引脚呈高阻态,此时在外部接入1个3.3V的上拉电阻,IO就可以输出3.3V了。开漏模式下,可以通过外接不同电压的上拉电阻来输出不同的电平。低电平和高阻态组成开漏输出。

1.5. 滤波电路

在直接电路系统中,因为各种干扰或是整流不够好,信号中依然会夹杂一些干扰波形。滤波电路就是为了去掉信号中的这些纹波干扰。滤波电路有非常多,常见的设计有电容滤波、电感滤波、复合滤波等。

1.5.1. 电容滤波

电容器的特点是对直流电表现出的阻抗极大,相当于不导通,对交流电,频率越高阻抗越小。利用电容器的这个特点可以将混杂在直流信号中的交流信号给过滤出来。电阻和电容构建的RC滤波器,有低通和高通滤波器之分,RC滤波器的截止频率的计算公式为:F(cutoff) = 1 / (2πRC)。

-

RC低通滤波,通过上面的公式可以计算下面的RC滤波器的截止频率1592Hz,只有低于这个频率的信号才能输出。

-

RC高通滤波,只有高于截止频率的信号才能输出。如麦克风中会附加有直流信号,这是无效信号,可以用高通滤波过滤掉。

3. RC带通滤波,即同时采用高通滤波和低通滤波,这样就可以输出指定频率范围内的信号。

1.5.2. 电感滤波

电感对频率较低的信号具有较低的阻抗,而对高频信号则表现出较高的阻抗。

截止频率的计算公式为:fc = 1 / (2πRL))

-

RL低通滤波

2. RL高通滤波

1.5.3. 复合滤波

复合滤波一般是指电容电感同时参与滤波,如LC带通滤波,因为L,C并联电路,电感和电容都是谐振频率为f0,只有频率为f0的信号可以通过LC带通滤波器到下一级电路。

1.5.4. 磁珠过滤

磁珠FB对高频过滤有更好的效果,对电磁抑制效果好,并且其有更低的功耗,尺寸小巧,相比RC/RL过滤,磁珠在高温高压下的可靠性更高。C2和C3、C4均是去耦电容,去耦电容主要用于滤除电源波动引起的高频噪声和纹波,稳定电源,减少开关噪声在电路板上的传播,并防止电源携带的噪声对电路构成干扰。

1.5.5. 电源去耦

电容有两个特性储能和滤波。电源在开头的瞬间会有剧烈的变化,可能对IC有较大的影响。去耦电源通过其储放电的特性,可以让电源开关的时候变得更平缓,不会一瞬间完成,这个工作主要由10uF极性电容来完成。0.1uF的小电容,对高频更敏感,主要是用来过滤高频信号的。两个电容都有储能滤波的功能,只是侧重点不同。

1.6. 阻抗匹配

输出与输入电路的等效电阻如果不匹配,就会导致电压电流分配的不均匀,进而会导致信号变化的时候发生反射,增加干扰等等,这种现象在高速传输都号中尤其重要,因为高速对信号的质量要求更高。一般建议认为在300MHz的信号速度下,需要考虑阻抗匹配。

阻抗匹配的方法:

-

PCB走线的宽度、形状(弯角、直角等)、距离等都影响阻抗大小,通过综合设计PCB的走线来实现阻抗匹配。

-

在数据线终端直接添加阻抗匹配电阻进行匹配。

1.7. MOS管与继电器

MOS管与继电器都可以用于控制电路中的电流开关。

-

MOS管是通过控制栅极电压来控制源极漏极导通实现对电流的开关,其响应级别为纳秒级,且其无机械部件,寿命可达上亿次,体积小,功耗小,适用于低电流电路。

-

继电器是通过电磁感应原理来实现机械的开断来实现对电流的开头,其响应级别多为毫秒级,且因为是机械部件,寿命在百万次(详细参考说明书),体积较大,功耗较大,高低负载电路均适用。

1.8. RS232和RS485

RS232和RS485包括接口与传输一整套电气和机械规范。UART更多指IC内部的一个模块,作用是将内部信号转换为串口协议的接口,与外设进行通信。PC端用于串口通信的接口,我们一般称为COM口。

1.8.1. RS232

RS232(Recommended Standard 232)是一种物理接口标准,根据RS232规范,传输距离在15米以内,常见的电压级别如下:

-

逻辑1: 在RS232中,逻辑1通常被定义为负电平(Negative Voltage Level)。具体的电压范围可以在-3V至-15V之间,其中约定更常见的是-12V作为逻辑1的电平。

-

逻辑0: 逻辑0则被定义为正电平(Positive Voltage Level),电压范围一般在+3V至+15V之间,其中约定更常见的是+12V作为逻辑0的电平。

所以RS232与TTL电平不兼容,需要电平转换器才能与支持TTL电平的设备通信。

1.8.2. RS485

RS485(Recommended Standard 485)是一种平衡式串行通信接口标准,主要用于工业自动化和楼宇自动化等需要长距离、高可靠性通信的应用。它是一种差分通信协议,这意味着它使用两根信号线(A和B)和一根接地线来传输数据,这样可以让信号更加稳定,传输更远的距离,实际测试有达到几千米。

-

逻辑“1”以两线间的电压差为+(2-6)V表示;

-

逻辑“0”以两线间的电压差为-(2-6)V表示。

所以, RS485与TTL电平兼容,不需要转换即可以与支持TTL电平的设备通信。

线缆长度小于100米,支持最大传输速度达10 Mbps;线缆长度小于1000米,支持最大传输速度达1 Mbps;线缆长度小于10公里,支持最大传输速度达100Kbps。

RS485速度快,信号稳定,可以用于总线传输。传输协议可以参考MODBUS协议,支持单播模式和广播模式。

1.9. 译码器

译码器的主要作用是将输入的编码信号转换为对应的输出信号。如下图38译码器(3-to-8 Decoder)是一种常见的数字逻辑电路,用于将3位二进制输入编码信号转换为8个输出信号中的一个激活状态。

1.10. UART、IIC和SPI

UART、IIC和SPI是常用的几种外设通信协议,多数IC会自带相关接口可以直接配置使用,如果没有配置,可以通过软件配置GPIO来实现通信。

1.10.1 UART

UART(通用异步收发器),这是用于全双工串行通信的最常见协议。UART一共用4根线,分别是数据发送线,数据接收线,VCC,GND。Vcc用于对外提供电源,一般可以不用。GND一般也可以不用,如果监控设备和UART同时接入一台电脑,GND可以不用接。如果监控设备设备与UART不在同一台电脑,需要接上GND作为参考地。

常用的UART是使用USB串口线,电脑安装串口驱动,就可以通过电脑串口设备与监控设备通信。

波特率(Baud rate)是衡量串行通信速度的指标,表示每秒传输的位数或符号数。它表示在单位时间内传输的数据量大小。例如,一个波特率为9600的UART通信表示每秒传输9600个位。

PL2303的串口转USB按说明文档最高支持1.2Mb/S,支持1152000的波特率。为了降低干扰,串口线尽量短一些。

通过UART让PC与设备进行通信,可以用于打印调试信息、控制设备、设备升级等。

1.10.2. IIC

IIC(Inter-Integrated Circuit)是一种串行通信协议,也被称为I2C(Inter-IC)总线,设备的SDA和SLC采用开漏输入,所以需要接上拉电阻。IIC是主从协议,EEPROM是支持IIC协议的从设备。高速 IIC 总线一般可达 400kbps 以上。

1.10.3. SPI

SPI(Serial Peripheral Interface)是一种高速、全双工的总线协议。NOR Flash(非易失性存储器闪存)可以通过SPI接口进行通信。

2. 眼图

2.1. 概念

当前计算机总线系统中,串行总线大行其道,有PCIe、USB、eMMC、UFC等。串行总线追求高速,对信号质量要求更高。通过不停采样大量超过一个周期的随机信号叠加显示,其图形如同一个眼睛,所以这种图形也被称为眼图(Eye Diagram/Eye Pattern)。眼图一般用于高速信号完整性分析。

2.2. 构成

单个引脚的输出电平受其前后电平的影响,所以其有8种可能情况。大量随机采集的信号,就由这8种信号构成,叠加显示就如下面的眼图。

2.3. 质量标准

-

除另有规定之外,下限和上限分别定为脉冲峰值幅度的10%和90%。

-

下降时间(Fall Time):脉冲信号的下降时间是指从脉冲峰值幅度的90%下降到10%所经历的时间间隔。

上冲(Overshoot):也叫过冲就是第一个峰值或谷值超过设定电压,主要表现为一个尖端脉冲,并且能导致电路元器件的失效。 -

下冲(Undershoot):是指下一个谷值或峰值。过分的过冲能够引起保护二极管工作,导致过早地失效。过分的下冲能够引起假的时钟或数据错误。

-

门限电平(Threshold/Crossing Percent):是指在系统传输特性劣于某一特定误码率的情况下,收信机所能达到的最低接收电平。

由于多次信号的叠加,眼图的信号线变粗,出现模糊(Blur)的现象。所以眼图也反映了信号的噪声和抖动:在纵轴电压轴上,体现为电压的噪声(Voltage Noise);在横轴时间轴上,体现为时域的抖动(Jitter)。如下图示。

一般会使用眼幅度、眼高度、品质因子、眼图交叉比等度量标准来分析眼图质量。

3. U盘电路

3.1. IC端

-

VCC和VCC3这两个都是去耦电路,并且在其中加了磁珠,这样可以更好地过滤高频信号。并且磁珠的可靠性好,能够提升电路的可靠性。

-

R2和R3是两个阻抗匹配电阻,防止信号反射,提升高速数据信号质量。

-

R4是一个上拉电阻。

-

R6是一个上拉电阻,并配置了一个发光二极管。

-

VCC、VCC3.3都接了1个小电压主要用于过滤高频信号的去耦电路。

文章来源:https://www.toymoban.com/news/detail-848074.html

文章来源:https://www.toymoban.com/news/detail-848074.html

3.2. Flash端

C122和C123用于电源去耦,提升电源质量。R50、R51、R52、R53、R54均是上拉电阻,针对输入式的IO提供默认的高电平。 文章来源地址https://www.toymoban.com/news/detail-848074.html

文章来源地址https://www.toymoban.com/news/detail-848074.html

到了这里,关于嵌入式开发——基础电路知识的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[嵌入式软件][启蒙篇][仿真平台] STM32F103实现串口输出输入、ADC采集](https://imgs.yssmx.com/Uploads/2024/01/814721-1.gif)