当我们在做项目的过程中,编写的底层Verilog代码不想交给甲方时怎么办呢?此时可以将源代码打包封装成网表文件(.qxp)进行加密,并且在工程中进行调用。

Quartus II的.qxp文件为QuartusII Exported Partition,用于创建综合或者PAR之后的网表文件。文章来源:https://www.toymoban.com/news/detail-848793.html

一、 .qxp文件打包封装步骤

- 在QuartusII的Project Navigator中选中欲创建qxp的module文件,右击,选择“Design Partition > Set as Design Partition”。

- 综合整个工程,想出PAR后的qxp就需要编译整个工程。

- 点击菜单“Process”,选择“Start > Start Partition Merge”,以创建完整的module网表。

- 点击菜单“Project”,选择“Export Design Partition”。

- 在弹出窗口中选择想要的层次和网表选项,即可导出.qxp文件。

二、示例

下面以按键控制LED灯的简单工程为例,展示网表文件封装的详细过程。

本工程用户代码模块分为三部分:文章来源地址https://www.toymoban.com/news/detail-848793.html

- key_filter.v:按键消抖模块代码

- keyLED.v:顶层设计文件

- led_control.v:LED灯控制模块

接下来将按键消抖模块key_filter.v封装为网表文件。

1、在QuartusII的Project Navigator中选中欲创建qxp的module文件,右击,选择“Design Partition > Set as Design Partition”。

选择“Design Partition > Set as Design Partition”之后,该module文件右上角会有一个品字形图标,如下:

2、全编译整个工程

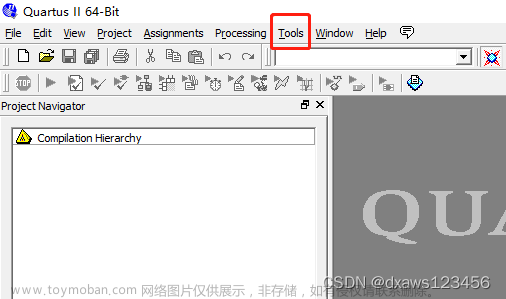

3、点击菜单“Processing”,选择“Start > Start Partition Merge”,以创建完整的module网表。

4、点击菜单“Project”,选择“Export Design Partition”。

5、在弹出窗口中选择想要的层次和网表选项,即可导出.qxp文件。

首先下拉选择要导出的模块,然后修改导出的文件名,点击OK完成导出,如下:

6、导出成功后,在工程目录下就会生成指定模块的一个.qxp文件,即网表文件

此时,将原本添加到此工程中的key_filter.v按键消抖模块删除,再将刚才封装好的.qxp网表文件添加进工程,实现网表文件导入。

还有另外一种导入.qxp文件的方式,如下:

点击菜单“Project”,选择“Import Design Partition”。

在弹出的窗口中选择要导入的Partition。

点击OK退出后以下会显示该网表文件的详细信息:

点击OK完成网表文件导入此工程,最后全编译Quartus工程,即可实现按键消抖模块的功能,此时本工程中以及删除掉了按键消抖功能的全部代码,只有按键消抖模块的网表文件。

以上就是网表文件封装的完整示例。

到了这里,关于【FPGA】Quartus18.1打包封装网表文件(.qxp)详细教程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!