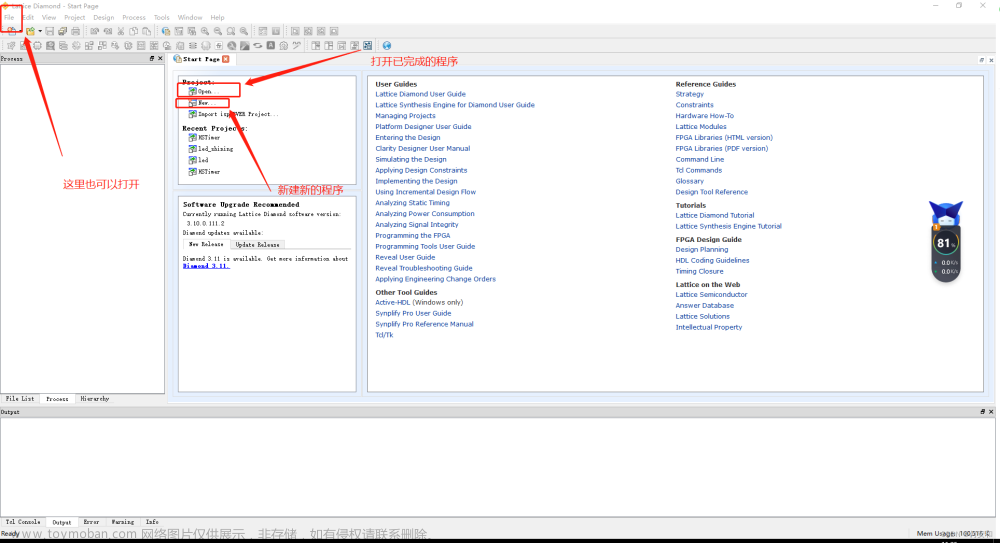

本文介绍Diamond开发软件进行IP核调用与对应官方文档查找方法。

1. IP核的调用

Diamond软件中,根据所选目标FPGA器件型号的不同,调用IP核的方式不同。共两种:一种是“IPexpress”;另一种是“Clarity Designer”。

IPexpress调用IP核:

Clarity Designer调用IP核:

接下来分别对两种情况的调用进行说明。

1.1 IPexpress调用IP核

1.点击“Tools”->“IPexpress”菜单,如下图所示,按照步骤配置IP核,Froject Path处选择存放IP文件的地址,可以事先建一个文件夹;

2.点击“Customize”后界面如下,进行IP核参数的配置,配置好后点击Generate,生成信息后colse关闭;

3.按照步骤根据自己的需求完成相应IP核的参数配置,点击“Close”完成配置。

4.将.ipx文件增加到工程中,将pll_ex_tmpl.v文件中的例化模板粘贴到顶层文件中即可实现IP的例化。

1.2 Clarity Designer调用IP核

点击“Tools”->“Clarity Designer”菜单进入“Clarity Designer”配置界面;

此时主要关注两个选项,一个是‘’Create new Clarity design‘’,一个是‘’Start Clarity Designer to generate a single Component SBX‘’均可以调用IP核,二选一。

两者的区别如下:

Create new Clarity design:可以同时配置多个IP核,将多个IP核的接口封装为一个模块。

例如我们将pll和mult核配置成一个块,此时看到生成的例化模板中将两个核的接口放在了一块。

集成块原理图:

集成块的例化模板:

Start Clarity Designer to generate a single Component SBX:配置单个IP核,与IPexpress调用IP核类似,一般选择此选项进行IP和调用。

由于选择‘’Start Clarity Designer to generate a single Component SBX‘’时调用IP核的方式与IPexpress调用IP核小节方法类似,只是会自动在工程中增加(.sbx)文件,只需在顶层中例化即可。所以接下来主要说明选择‘’Create new Clarity design‘’进行调用的方法。

1.点击“Tools”->“Clarity Designer”菜单进入“Clarity Designer”配置界面,完善库名路径设置之后点击“Create”,进入下图所示界面;

2.选择使用的IP核进行配置和IPexpress的类似,如下图所示;

3.这里你会发现可以同时配置多个IP核,配置多个IP核后如下图所示,可以查看原理图;

4.进入原理图界面如图所示;

5.如果要更改IP核的配置,鼠标右键点击模块,选择Config后进入配置页面更改;

6.点击“Generate”之后,项目文件自动会添加生成的库(.sbx)如下图所示;

7.将xx_tmpl.v文件中的例化模板粘贴到顶层文件中即可实现IP的例化。

参考:LATTICE入门篇之IP核

2. IP核相关文档查找

2.1 方法一

在调用IP核时,核选择页面点击需要使用的IP核,会在右端出现About页面,在页面最下方有对应的IP核官方文档可供查看学习。

2.2 方法二

调用IP核时,在IP核的配置界面按F1跳转到网页文档处;

跳转网页如图,点击对应文档查看。

2.3 方法三

直接在Diamond的安装目录下位置有支持的IP核网页文件,选择需要查看的IP核后跳转到网页中;

D:\Diamond\diamond\3.13\docs\webhelp\eng\Reference Guides\IPexpress Modules

IP的HTM文件。

3 问题

博主在使用中出现IP核在顶层例化综合后层级不改变的问题,暂时还不知道什么原因导致。

暂时解决办法:将生成的核文件中的.v文件增加到工程中综合,会出现报错但层级关系变正确。再移除调.v文件再次综合后是正确的层级关系。

文章来源:https://www.toymoban.com/news/detail-849166.html

文章来源:https://www.toymoban.com/news/detail-849166.html

📣您有任何问题,都可以在评论区和我交流📃!

📣本文由 YprgDay 原创,首发于CSDN平台🐵,博客主页:YprgDay的主页

📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!文章来源地址https://www.toymoban.com/news/detail-849166.html

到了这里,关于【Lattice FPGA 开发】IP核的调用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!