实验三的前两个实验:

- 国标码转区位码

- 汉字GB2312编码

在很多地方都找得到,我就不多说。

附上我使用过的连接:https://blog.csdn.net/gemingshun/article/details/106784595

其中我们老师提供的关于汉字字符集编码查询;中文字符集编码:GB2312、BIG5、GBK、GB18030、Unicode 的网址:https://www.qqxiuzi.cn/bianma/zifuji.php

好的接下来进入正题,关于该实验的第三个小实验具体步骤如下:

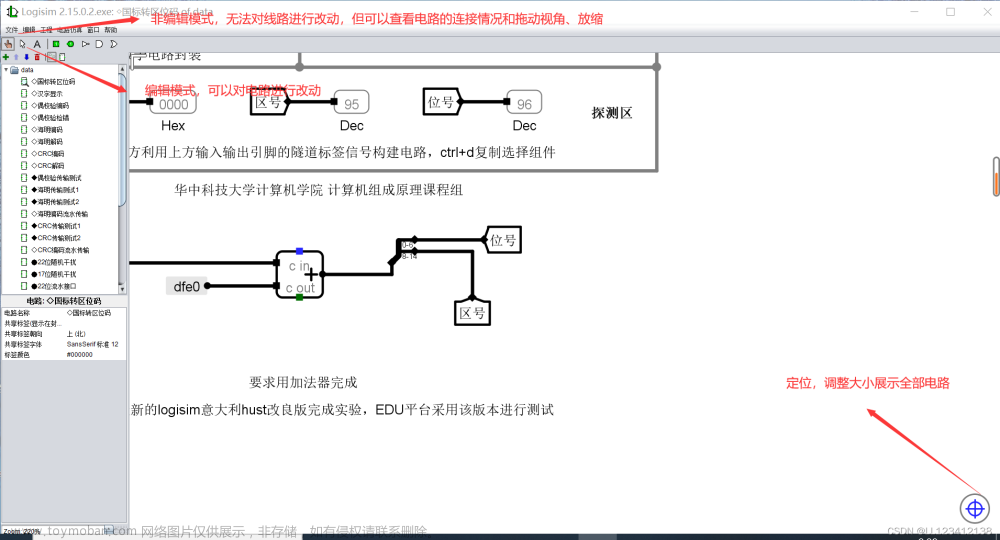

首先,打开data.circ(我在完成前两个试验时改了名字为data.1)文件中的“偶校验编码”,进行连线,(注意是 或门,针脚是16个;下一个小步骤里用的就是 异或门 了,针脚是17个 )

连线完成之后可以点击左上角“原始数据”里的每一位来进行监测,看电路是否会有深绿/浅绿的变化,“原始数据”的每一位数都对应图中的一根电路。

大家可以注意一下左上角的0,1变化,然后第一个小步骤就完成了

然后,点开“偶校验检错”,连成电路图如下图(异或门,17针脚):

(注意P1的两个结点不要冲合在一起了,我之前就是想着美观合在一起,结果好像就有点儿问题,具体原因我也不清楚)

然后电路图就算连接完成了,然后同样也是可以通过左上角的“输入引脚区”点击数字进行0,1的改变,再观察右上角的“检错位”的0,1变化来监测电路是否成功被连接。

奇数个浅绿电路检错位会显示为1,偶数个浅绿电路检错位会显示为0

于是第二个小步骤也完成咯

文章来源地址https://www.toymoban.com/news/detail-849377.html

最后,进入“偶校验传输测试”,直接来一个最终的测试就可以了

不断点击左上角的“时钟”,可以观察到左右两个红色大字的变化,也可以用快捷键Ctrl+K来进行连续的观察字的变化。如果前面电路连接正确的话右侧的灯应该是会出现三种情况:

第一种,就是传输过程中没有错误,左右两边的字是一致的,即“检错位”不亮灯,“数据正确”亮绿灯

第二种,就是有奇数个错误,检错位能够帮你识别出来,即“检错位”亮红灯

第三种,就是有偶数个错误,偶校验是无法检测出偶数个错误的,即“误报”亮绿灯

最后,就没有最后了呗,截图写实验报告去!!

欢迎大家评论区指出错误,减少他人走弯路的次数文章来源:https://www.toymoban.com/news/detail-849377.html

到了这里,关于计算机组成原理实验logisim(三)之偶校验编码与检错的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!