目录

create_clcok

source_objects

-name

-period

-waveform

-add

create_generated_clock

-source

-master_clock

-edge

-divide_by / multiply_by

-combi

-add

create_clcok

Create Clock (create_clock)约束可以定义设计中时钟的属性和要求,必须定义时钟约束以确定设计的性能并限制进入 FPGA 的外部时钟。

指定约束所应用的 Clock name (-name),时钟 Period (-period),上升和下降 Waveform edge 值(-waveform)和目标信号。

create_clock

[source_objects]

[-period period_value]

[-waveform edge_list]

[-name clock_name]

[-add]

以下命令创建一个 5ns 周期的 sys_clk 时钟,并将此时钟应用于 CK2 端口:

create_clock

[get_ports CK2]

-period 5.0

-waveform {1.0 2.0}

-name sys_clksource_objects

source_object是设计中时钟存在的位置,通常是输入端口,但也可以是设计内部的引脚。get_ports指这个hierarchy的端口,特指input/output/inout信号,引脚信号只能用get_pins。

如果不指定源对象,则定义一个虚拟时钟,它是用作设置输入延迟和输出延迟的参考的时钟,但在设计中物理上并不存在。

create_clock -name clkesc -period 50.0 -waveform {0.0 25.0}-name

-name后跟的时钟名并非真正RTL里的时钟名,而是该sdc中的时钟名字,用于在这份sdc中指代这个时钟,后续例如set_group/set_clock_uncertainty都会直接用这个name来指定这个时钟。

set_clock_groups -asynchronous -group {sys_clk}-period

每个时钟都应使用该-period选项定义其周期,这是相同波形端到端重复的时间段,默认情况下,时钟具有 50% 的占空比,在时间零处有上升沿,在周期的二分之一处有下降沿。

-waveform

如果时钟并非50%占空比,可以使用选项指定波形-waveform,并提供时钟周期内的上升沿和下降沿时间列表。例如,以下命令创建一个具有默认波形的时钟和另一个上升沿为 1.0、下降沿为 2.0 的时钟。派生时钟波形如下所示。

create_clock -period 5.0 [get_ports CK1]

create_clock -period 5.0 -waveform {1.0 2.0} [get_ports CK2]

-add

-add选项允许将多个时钟添加到设计中的同一源对象。例如,如果要以两个不同的频率驱动同一时钟输入,可以使用以下命令:

create_clock -period 10 -name clk_100 [get_ports clk_sys]

create_clock -period 5 -name clk_200 [get_ports clk_sys] -add尽管对一个端口定义两个以上的基本时钟并不常见,如果有需要,确保在第一个时钟之后对所有时钟指定-add。

create_generated_clock

Create Generate Clock (create_generated_clock)约束使用于定义设计中内部派生时钟的属性和约束,可以指定 Clock name (-name),时钟派生的 Source node (-source)和 Relationship to the source 属性,对为修改时钟信号属性的任何节点定义派生时钟,包括修改相位,频率,偏移或占空比,工具根据主时钟确定派生时钟特性,如果主时钟的周期或延迟发生变化,则派生时钟也会相应变化。

如下命令创建了一个名为 cfg_clk 的时钟,这个时钟的source为一个名为 cfg_clk 的端口,应用于 cfg_clk_CONST_BUF/Z 引脚,并且它是依赖于一个现存的时钟(同时也被命名为 cfg_clk)。

create_generated_clock -name cfg_clk [get_pins cfg_clk_CONST_BUF/Z] -source [get_ports cfg_clk] -master_clock [get_clocks cfg_clk] -combi -add-source

-source 选项指定时钟路径中节点的名称,用作generated clock的参考。generated clock的时钟源必须是设计网表中的节点,而不是先前定义的时钟的名称。可以在generated clock的目标的输入时钟管脚与其参考时钟的目标节点之间的时钟路径上使用任何节点名称作为source。

如下命令创建了一个名为pclk的派生时钟,source在端口pclk上,派生时钟的引脚为cdphyrx_pclk_CONST_BUF/Z。

create_generated_clock -name pclk [get_pins cdphyrx_pclk_CONST_BUF/Z] -source [get_ports pclk]-master_clock

如果有多个基本时钟驱动一个作为派生时钟的source,则必须定义多个派生时钟,可以在每个派生时钟语句中使用-master_clock 选项将每个派生时钟与一个基本时钟相关联。在某些情况下,派生时钟使用组合逻辑生成。

create_generated_clock -name rxwordclkhs_d0_div2 -source [get_pins u_ppi/u_widedata_d0/div_clk_reg_0_/Q] -master_clock [get_clocks hsrx_word_clk_d0_div2] [get_pins rxwordclkhs_0_CONST_BUF/Z] -master_clock实际上就是-source的时钟名称,所以-master_clock用的是get_clock,即create_(generated_)clock时-name后跟的时钟名称,而source用的get_pins/get_ports。

create_generated_clock -name hsrx_word_clk_d0_div2 -edges {1 3 5} -source [get_pins u_core/o_rxwordclkhs_d0] [get_pins u_ppi/u_widedata_d0/div_clk_reg_0_/Q]

create_generated_clock -name rxwordclkhs_d0_div4 -add -edges {1 2 3} -source [get_pins u_ppi/u_widedata_d0/div_clk_reg_1_/Q] -master_clock [get_clocks hsrx_word_clk_d0_div4] [get_pins rxwordclkhs_0_CONST_BUF/Z] -source/-master只对紧跟的命令有效,如上面的第二条命令,-master_clock为hsrx_word_clk_d0_div4,再后面跟的get_pins实际上是派生时钟的引脚。

-edge

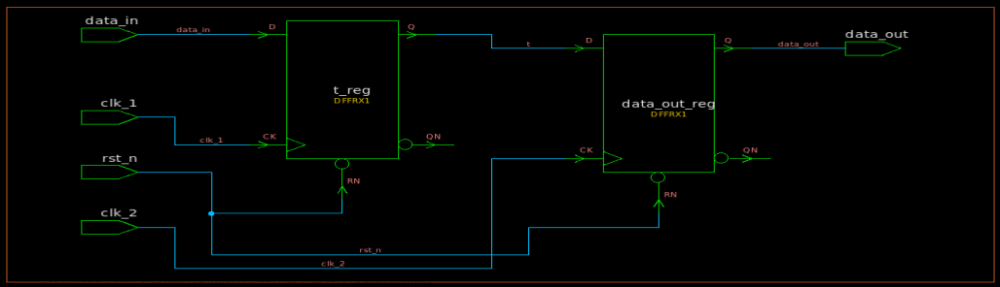

使用 create_generated_clock -edges 可以根据主引脚上主时钟波形的边沿来指定派生时钟,例如下图所示的时钟发生器电路。

派生时钟信号DIV3A的周期是主时钟的三倍,并且具有不对称波形。要指定此波形,可以使用

create_ generated_clock -edges { 1 5 7 } \

-name DIV3A -source [get_ports SYSCLK] [get_pins U2/Q]有时generated时没有明确写出分频时,可以从-edge判断分频,如下命令,rxclkesc_out_d0为cb_lp_dco_clk的19分频。

create_generated_clock -name rxclkesc_out_d0 -add \

-edges {1 19 39} -source [get_pins u_core/cb_lp_dco_clk] \

-master_clock [get_clocks cb_lp_dco_clk] [get_pins u_core/rxclkesc_out_d0]

-divide_by / multiply_by

下图显示了 2 分频派生钟的示例,时钟波形和二分频时钟发生器生成的时钟波形。要指定分频时钟,请使用命令-divide_by选项create_generated_clock并指定分频因子。

create_ generated_clock -name DIVIDE \

-source [get_ports SYSCLK] -divide_by 2 [get_pins FF1/Q]指定一个端口或引脚(不是时钟名称)作为生成新时钟的source,指定一个引脚作为派生时钟的创建点。

请注意,派生时钟沿基于主时钟源引脚(通过选项指定-source)出现的上升沿。如果您需要根据主时钟源引脚的下降沿创建派生时钟,请使用 选项-edges而不是 选项-divide_by。

multiply_by和divide_by的使用方式一样,一个为倍频,一个为分频。

-combi

在时序分析期间,当该工具计算派生时钟的时钟源延迟时,它会跟踪派生时钟的源引脚与其主时钟的源引脚之间的组合路径和时序路径。时序路径是包含寄存器时钟引脚、透明锁存器的数据引脚或除路径中的最终引脚之外的生成时钟定义点的任何路径。

create_ generated_clock -name CLK_INV \

-source [get_ports CLK] -divide_by 1 [get_pins A/Y] \

-combinational当指定此选项时,生成的时钟与主时钟具有相同的周期。-combinational只能对那些分频(-divide_by 1)或倍频(-multiply_by 1)的时钟使用该选项。文章来源:https://www.toymoban.com/news/detail-849766.html

-add

和create_clock时一样的用法,如果在同一个pin/port的位置生成了多个派生时钟,第二个及之后的派生时钟需要添加加-add。文章来源地址https://www.toymoban.com/news/detail-849766.html

到了这里,关于SDC学习之create_(generated_)clock的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!