1. 官方文档查找链接

搜索结果 • AMD 自适应计算文档门户 (xilinx.com)

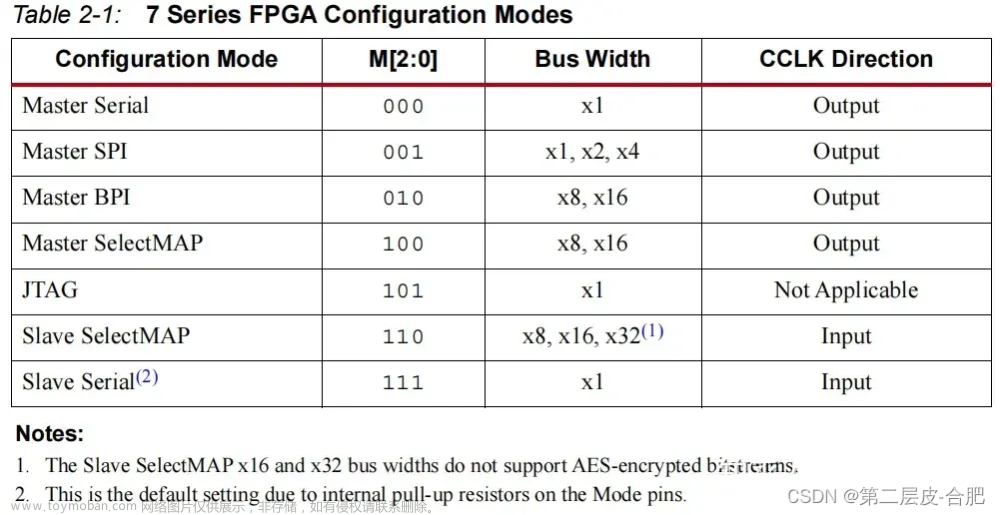

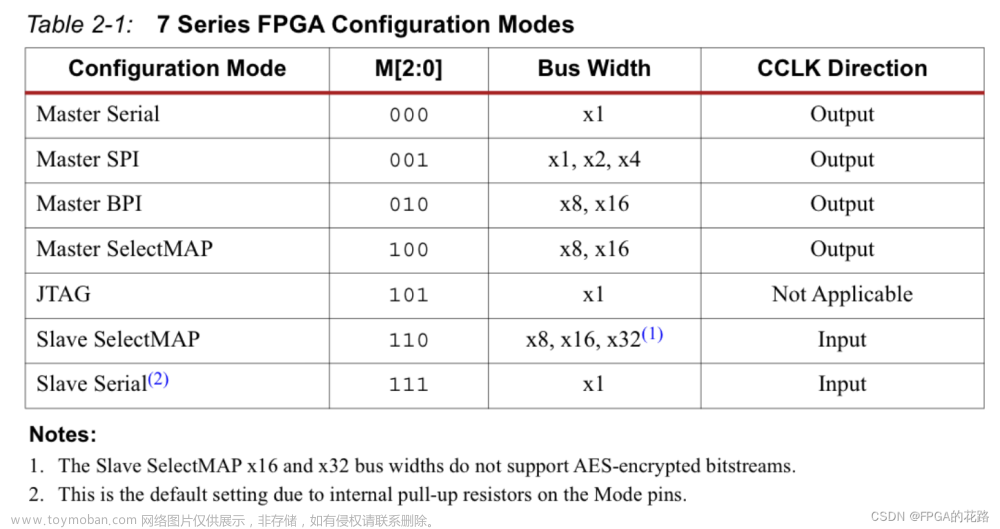

2. ug470 - 配置user guide

7 Series FPGAs Configuration User Guide • 7 Series FPGAs Configuration User Guide (UG470) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

3. ug471 -IO资源

ug471_7Series_SelectIO.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

2. ug472 - 时钟资源

ug472_7Series_Clocking.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

3. ug473 - 存储资源(BRAM)

ug473_7Series_Memory_Resources.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

4. ug474 - 逻辑资源

ug474_7Series_CLB.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

5. ug475 - 管脚资源

ug475_7Series_Pkg_Pinout.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

6. ug476 - GTX/GTH高速收发器

ug476_7Series_Transceivers.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

7. ug477 - PCIe IP核

ug477_7Series_IntBlock_PCIe.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

8. ug478 没找到

9. ug479 - DSP48

ug479_7Series_DSP48E1.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com)

10. ug480 - XADC

XADC : 模数转换,FPGA电压,温度监控

7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide (UG480) • 7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide (UG480) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)文章来源:https://www.toymoban.com/news/detail-849947.html

xilinx 7系列FPGA之XADC的学习笔记_weichen001122的博客-CSDN博客文章来源地址https://www.toymoban.com/news/detail-849947.html

到了这里,关于xilinx 7系列FPGA 官方文档整理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!