AD9361纯逻辑FPGA驱动,单音信号收发例程,可动态配置9361,verilog代码,Vivado 2019.1工程。

在当前高度发达的科技时代,FPGA(Field Programmable Gate Array)已成为在数字电子领域中广泛应用的关键技术之一。FPGA作为一种可编程的集成电路,具备了硬件级的性能和灵活性,被广泛用于数字信号处理、通信、嵌入式系统等领域。其中,AD9361是一款常见的射频收发器模块,其结合了灵活的收发功能和可配置的数字接口,为无线通信应用提供了重要支持。

本文将围绕着AD9361纯逻辑FPGA驱动展开探讨,重点介绍单音信号收发例程的设计与实现。此例程具有动态配置AD9361的功能,基于verilog代码实现,并在Vivado 2019.1工程中完成。需要特别指出的是,本产品为FPGA代码,由于其特殊性质,不支持退换货,请在使用前慎重考虑。

首先,让我们深入了解AD9361纯逻辑FPGA驱动的背景和关键特性。AD9361作为一款高性能的射频收发器模块,具备了多种调制和解调技术,实现了广泛的通信标准和频率范围的支持。其集成了本地振荡器、低噪声放大器、混频器等功能模块,能够满足无线通信中的多种需求。

在FPGA中驱动AD9361的过程中,单音信号收发例程的设计显得尤为重要。该例程旨在实现单音信号的接收和发送,并能够动态配置AD9361的相关参数。通过verilog代码编写,可以灵活地控制FPGA与AD9361之间的数据交互和信号处理。同时,借助Vivado 2019.1工程,可以提供便捷的开发环境和可视化的设计流程,加快开发效率。

在实际设计中,我们需要根据具体的应用场景和需求来选择合适的收发模式和参数配置。AD9361提供了丰富的配置选项,包括中心频率、带宽、增益等,可以根据不同情况进行调整。通过动态配置AD9361,我们能够适应不同的通信标准和频率要求,提高系统的灵活性和适应性。

为了更好地理解其工作原理,我们需要对verilog代码进行分析和解读。verilog是一种硬件描述语言,用于描述数字电路和系统级集成电路的行为和结构。通过详细分析verilog代码,我们可以了解到单音信号收发例程与AD9361之间的数据交互方式,以及各个模块之间的逻辑关系。这对于深入理解整个系统的工作原理和性能优化非常重要。

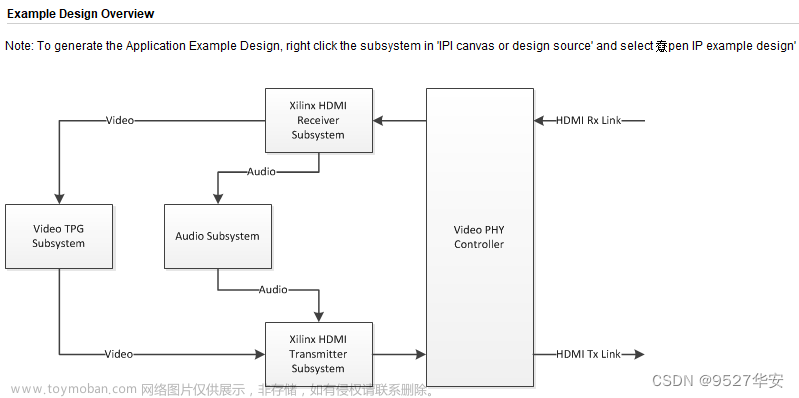

在进行FPGA设计和开发时,利用Vivado 2019.1工程能够极大地提高开发效率。Vivado是由Xilinx公司开发的一款集成开发环境(IDE),适用于FPGA设计和开发。它提供了丰富的工具和资源,如IP核生成、约束管理、时序分析等,可以帮助程序员更好地完成AD9361纯逻辑FPGA驱动的设计和验证。

需要注意的是,由于本产品为FPGA代码,与传统的软件产品有所不同,不支持退换货。因此,在选择和使用本产品时,请仔细衡量其适用性和可行性,确保符合系统设计和需求。

综上所述,本文围绕AD9361纯逻辑FPGA驱动展开,重点介绍了单音信号收发例程的设计与实现。通过verilog代码编写和Vivado 2019.1工程支持,我们能够实现对AD9361的动态配置,并灵活地适应不同的通信标准和频率要求。需要特别强调的是,本产品为FPGA代码,不支持退换货,请在使用前慎重考虑。通过阅读本文,您将更好地文章来源:https://www.toymoban.com/news/detail-850041.html

相关代码,程序地址:http://imgcs.cn/lanzoun/752846103385.html

文章来源地址https://www.toymoban.com/news/detail-850041.html

到了这里,关于AD9361纯逻辑FPGA驱动,单音信号收发例程,可动态配置9361的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!