好物分享:FPGA实现SDI视频编解码的方案设计汇总

1、前言

目前FPGA实现SDI视频编解码有两种方案:一钟是使用专用SDI编解码芯片,另一种是使用FPGA;两者主要区别如下:

2、专用芯片方案

目前SDI编解码专用芯片方案市场主导厂家是Semtech和TI,其中Semtech占有率高于TI,我用过的只有Semtech公司的GS2971和GS2972,暂未用过TI的芯片,以后有机会也会涉足TI的方案;当然,还有诸如海思之类的国产IC公司也在涉足改领域,但目前还不是主流;

GS2971和GS2972一般是成对使用,GS2972负责编码发送SDI,GS2971负责解码接收SDI,该方案在消费电子领域占有主导市场,比如某宝几十块钱的HDMI与3G-SDI的转换盒,当然,在广播电视、医疗、军工等领域也有广泛应用,但这些领域一般会搭配强大的主控芯片,所以产品价格一般较贵;

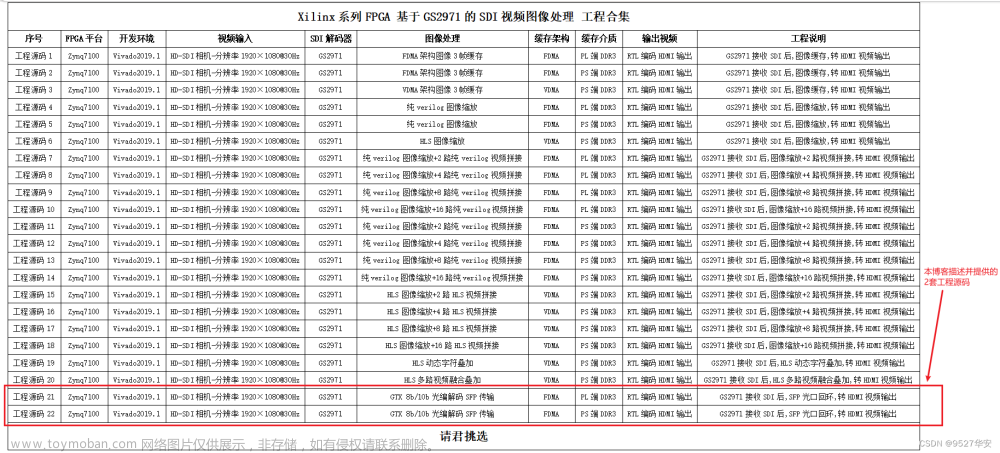

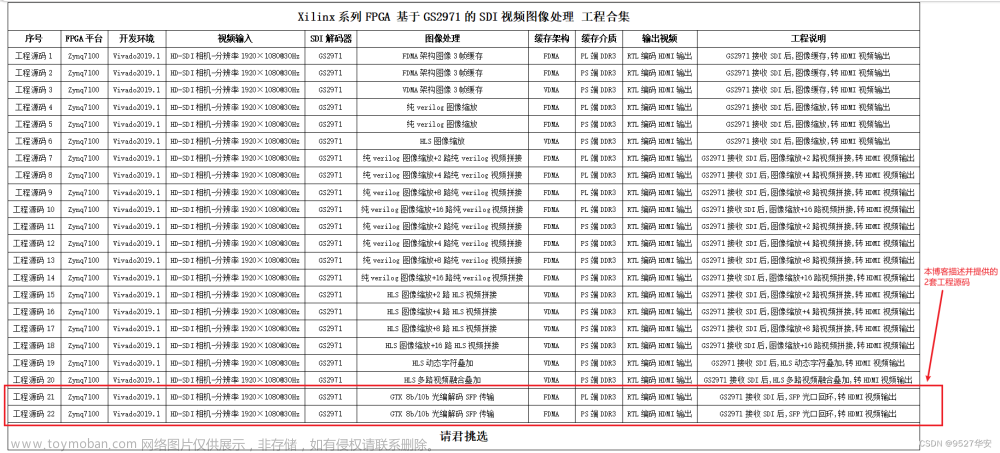

本博不是做硬件电路的,只会看看原理图和芯片手册,更多的还是做GS2971/GS2972基于FPGA的开发应用;GS2971/GS2972搭配FPGA一般应用在医疗或军工领域,或可GS2971+FPGA实现SDI图像采集传输板卡;或可GS2972+FPGA实现SDI工业相机,或可GS2971+GS2972+FPGA实现SDI综合图像处理板卡;有此类项目需求的朋友,推荐本博现有的GS2971/GS2972基于FPGA的开发应用如下:

2.1、GS2971+FPGA的图像采集 设计方案

该项目SDI接收方案采用GS2971,FPGA采用Xilinx的Zynq7100-xc7z100ffg900-2;Zynq7100的PL端为Kintex7-325T,PS端为ARMxx,所以既可以把Zynq7100当作纯FPGA来使用,比如Xilinx的Artix7、Kintex7、Vrtix7、KU、VU等,也可以当作Zynq来使用,比如Xilinx的Zynq7000系列、Zynq UltraScale、Zynq UltraScale+,甚至可以当作国产复旦微、紫光、高云、易灵思、安陆等FPGA来使用;基于此,这个方案设计了两种架构,一种是纯FPGA架构,另一种是Zynq架构,两种方案的区别在于图像缓存方式的差异;纯FPGA架构图像缓存采用MIG+PL端DDR3方式,FPGA架构图像缓存采用Zynq HP接口+PS端DDR3方式;

该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

其中FDMA图像缓存版本的工程设计原理框图如下:

VDMA图像缓存版本的工程设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.2、GS2971+FPGA的图像采集+图像缩放 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了图像缩放功能,属于SDI图像处理范畴,适用于有图像缩放需求的中高端项目;设计了两种图像缩放方案,一种是纯verilog实现的,另一种是HLS实现的,但两种图像缩放方案的功能都是一样的,都能实现任意尺寸的缩放,即无极缩放;该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

纯verilog实现的图像缩放版本设计原理框图如下:

HLS实现的图像缩放版本设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.3、GS2971+FPGA的图像采集+纯verilog图像缩放+纯verilog视频拼接 设计方案

该方案在2.2章节《GS2971+FPGA的图像采集+图像缩放 设计方案》的基础上加了视频拼接功能,属于SDI图像处理范畴,适用于有图像缩放+视频拼接需求的高端项目;该设计使用纯verilog实现的图像缩放+纯verilog实现的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供16套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.4、GS2971+FPGA的图像采集+HLS图像缩放+Video Mixer视频拼接 设计方案

该方案在2.3章节《GS2971+FPGA的图像采集+纯verilog图像缩放+纯verilog视频拼接 设计方案》的基础上替换了图像缩放和视频拼接方案,属于SDI图像处理范畴,适用于有图像缩放+视频拼接需求的高端项目;该设计使用自研的HLS实现的图像缩放+Xilinx官方的Video Mixer IP Core的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供4套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.5、GS2971+FPGA的图像采集+OSD动态字符叠加 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了OSD动态字符叠加功能,属于SDI图像处理范畴,适用于有OSD动态字符叠加需求的高端项目;该设计使用自研的HLS实现的OSD动态字符叠加方案;可实时的、动态修改字符信息,在军工领域应用广泛;该方案提供1套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.6、GS2971+FPGA的图像采集+视频融合叠加 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了视频融合叠加功能,属于SDI图像处理范畴,适用于有视频融合叠加需求的高端项目;该设计使用自研的HLS实现的视频融合叠加方案;可实时的融合并叠加并显示两路SDI视频,在军工领域应用广泛;该方案提供1套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.7、GS2971+FPGA的图像采集+GTX 8b/10b编解码高速接口 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了GTX高速接口功能,属于SDI图像处理范畴,适用于有GTX高速接口需求的高端项目;该设计使用Xilinx的GTX高速接口方案;可将采集的SDI视频通过GTX 8b/10b编解码的高速接口传输,在军工领域应用广泛;该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.8、GS2971+FPGA的图像采集+PCIE高速接口 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了PCIE高速接口功能,属于SDI图像处理范畴,适用于有PCIE高速接口需求的高端项目;该设计使用Xilinx的XDMA方案和非Xilinx的RIFFA方案;可将采集的SDI视频通过PCIE高速接口传输到PC,并在PC端通过QT上位机显示图像,在军工领域应用广泛;该方案目前还在调试中,敬请期待本博推出。。。

2.9、GS2971+GS2972+FPGA的图像采集 设计方案

该方案在2.1章节《GS2971+FPGA的图像采集 设计方案》的基础上加了GS2972输出SDI功能,属于SDI图像传输,适用于有SDI接收+SDI发送的高端项目;该设计使用GS2971接收SDI、GS2972发送SDI,依然采用FDMA和VDMA图像缓存方案,该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

其中FDMA图像缓存版本的工程设计原理框图如下:

VDMA图像缓存版本的工程设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.10、GS2971+GS2972+FPGA的图像采集+图像缩放 设计方案

该方案在2.2章节《GS2971+FPGA的图像采集+图像缩放 设计方案》的基础上加了GS2972输出SDI功能,属于SDI图像处理范畴,适用于有SDI视频收发+图像缩放需求的中高端项目;设计了两种图像缩放方案,一种是纯verilog实现的,另一种是HLS实现的,但两种图像缩放方案的功能都是一样的,都能实现任意尺寸的缩放,即无极缩放;该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

纯verilog实现的图像缩放版本设计原理框图如下:

HLS实现的图像缩放版本设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.11、GS2971+GS2972+FPGA的图像采集+纯verilog图像缩放+纯verilog视频拼接 设计方案

该方案在2.3章节《GS2971+FPGA的图像采集+纯verilog图像缩放+纯verilog视频拼接 设计方案》的基础上加了GS2972输出SDI功能,属于SDI图像处理范畴,适用于有SDI视频收发+图像缩放+视频拼接需求的高端项目;该设计使用纯verilog实现的图像缩放+纯verilog实现的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供16套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.12、GS2971+GS2972+FPGA的图像采集+HLS图像缩放+Video Mixer视频拼接 设计方案

该方案在2.4章节《GS2971+FPGA的图像采集+HLS图像缩放+Video Mixer视频拼接 设计方案》的基础上加了GS2972输出SDI功能,属于SDI图像处理范畴,适用于有SDI视频收发+图像缩放+视频拼接需求的高端项目;该设计使用自研的HLS实现的图像缩放+Xilinx官方的Video Mixer IP Core的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供4套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.13、GS2971+GS2972+FPGA的图像采集+OSD动态字符叠加 设计方案

该方案在2.5章节《GS2971+FPGA的图像采集+OSD动态字符叠加 设计方案》的基础上加了GS2972输出功能,属于SDI图像处理范畴,适用于有SDI视频收发+OSD动态字符叠加需求的高端项目;该设计使用自研的HLS实现的OSD动态字符叠加方案;可实时的、动态修改字符信息,在军工领域应用广泛;该方案提供1套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.14、GS2971+GS2972+FPGA的图像采集+视频融合叠加 设计方案

该方案在2.6章节《GS2971+FPGA的图像采集+视频融合叠加 设计方案》的基础上加了GS2972输出功能,属于SDI图像处理范畴,适用于有SDI视频收发+视频融合叠加需求的高端项目;该设计使用自研的HLS实现的视频融合叠加方案;可实时的融合并叠加并显示两路SDI视频,在军工领域应用广泛;该方案提供1套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.15、GS2971+GS2972+FPGA的图像采集+GTX 8b/10b编解码高速接口 设计方案

该方案在2.7章节《GS2971+FPGA的图像采集+GTX 8b/10b编解码高速接口 设计方案》的基础上加了GS2972输出功能,属于SDI图像处理范畴,适用于有SDI视频收发+GTX高速接口需求的高端项目;该设计使用Xilinx的GTX高速接口方案;可将采集的SDI视频通过GTX 8b/10b编解码的高速接口传输,在军工领域应用广泛;该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

2.16、GS2971+GS2972+FPGA的图像采集+PCIE高速接口 设计方案

该方案在2.8章节《GS2971+FPGA的图像采集+PCIE高速接口 设计方案》的基础上加了GS2972输出功能,属于SDI图像处理范畴,适用于有SDI视频收发+PCIE高速接口需求的高端项目;该设计使用Xilinx的XDMA方案和非Xilinx的RIFFA方案;可将采集的SDI视频通过PCIE高速接口传输到PC,并在PC端通过QT上位机显示图像,反过来,也可以通过PC端的QT上位机采集PC的图像传到FPGA并通过GS2972发送SDI视频,在军工领域应用广泛;该方案目前还在调试中,敬请期待本博推出。。。

3、Xilinx Kintex7系列FPGA 方案

Xilinx Kintex7系列FPGA拥有成熟的SDI逻辑编解码方案,该方案的核心是采用Xilinx官方的GTX+SMPTE SD/HD/3G SDI IP核架构,其中,GTX负责SDI视频的高速差分信号与并行信号的转换,本博称之为解串与串化;SMPTE SD/HD/3G SDI负责并行的SDI视频与BT1120视频的转换;相应的,Xilinx官方也给出了硬件电路参考设计,包括差分时钟设计、驱动器与均衡器设计等;

本博不是做硬件电路的,只会看看原理图和芯片手册,更多的还是做Xilinx Kintex7系列FPGA的SDI视频编解码开发应用;基于上述原理,Xilinx Kintex7系列FPGA可实现SDI图像采集传输板卡、可实现SDI工业相机、可实现SDI综合图像处理板卡等项目;有此类项目需求的朋友,推荐本博现有的Xilinx Kintex7系列FPGA的SDI视频编解码开发应用如下:

3.1、K7 FPGA的SDI视频编解码 设计方案

该项目采用Xilinx Kintex7-523T FPGA为平台,采用GTX+SMPTE SD/HD/3G SDI IP核架构接收3G-SDI视频,经过FDMA图像缓存后通过HDMI或SDI视频输出,该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

其中HDMI输出版本的工程设计原理框图如下:

SDI输出版本的工程设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.2、K7 FPGA的SDI视频编解码+图像缩放 设计方案

该方案在3.1章节《K7 FPGA的SDI视频编解码 设计方案》的基础上加了图像缩放功能,属于SDI图像处理范畴,适用于有SDI视频收发+图像缩放需求的高端项目;该方案使用纯verilog实现的图像缩放,能实现任意尺寸的缩放,即无极缩放;该方案提供3套vivado2019.1版本的工程源码,设计原理框图如下:

其中HDMI输出版本的工程设计原理框图如下:

SDI输出版本的工程设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.3、K7 FPGA的SDI视频编解码+图像缩放+视频拼接 设计方案

该方案在3.2章节《K7 FPGA的SDI视频编解码+图像缩放 设计方案》的基础上加了视频拼接功能,属于SDI图像处理范畴,适用于有SDI视频收发+图像缩放+视频拼接需求的高端项目;该设计使用纯verilog实现的图像缩放+纯verilog实现的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供8套vivado2019.1版本的工程源码,设计原理框图如下:

其中HDMI输出版本的工程设计原理框图如下:

SDI输出版本的工程设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.4、K7 FPGA的SDI视频编解码+图像缩放+UDP网络视频传输 设计方案

该方案在3.2章节《K7 FPGA的SDI视频编解码+图像缩放 设计方案》的基础上加了UDP网络视频传输功能,属于SDI图像传输范畴,适用于有SDI视频收发+图像缩放+UDP网络视频传输需求的高端项目;该设计使用纯verilog实现的图像缩放+UDP网络视频传输方案;FPGA接收3G-SDI视频后经过图像缩放后以UDP协议栈方式将视频发送到PC,PC端用QT上位机接收并显示图像;该方案提供1套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.5、K7 FPGA的SDI视频编码发送 设计方案

该方案的目的是将非SDI视频转换为SDI视频发送,也就是实现SDI相机的功能,非SDI视频可以是FPGA内部实现的动态彩条、廉价的OV5640、OV7725等,也可以是HDMI、PAL、CmeraLink等视频;FPGA采集到非SDI视频后进行图像缓存,然后通过SDI方式将视频输出;该方案提供10套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.6、K7 FPGA的SDI视频编码发送+图像缩放+视频拼接 设计方案

该方案在3.5章节《K7 FPGA的SDI视频编码发送 设计方案》的基础上加了图像缩放+视频拼接功能,属于SDI图像处理范畴,适用于有SDI视频发送+图像缩放+视频拼接需求的高端项目;该设计使用纯verilog实现的图像缩放+纯verilog实现的视频拼接方案;设计了2路、4路、8路、16路等多种视频缩放拼接方案;该方案提供8套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

3.7、K7 FPGA的SDI视频编解码+GTX 8b/10b编解码高速接口 设计方案

该方案在3.5章节《K7 FPGA的SDI视频编码发送》的基础上加了GTX高速接口功能,属于SDI图像处理范畴,适用于有GTX高速接口需求的高端项目;该方案提供套vivado2019.1版本的工程源码,该方案目前还在调试中,敬请期待本博推出。。。

3.8、K7 FPGA的SDI视频编解码+PCIE高速接口 设计方案

该方案在3.1章节《K7 FPGA的SDI视频编解码 设计方案》的基础上加了PCIE高速接口功能,属于SDI图像处理范畴,适用于有PCIE高速接口需求的高端项目;该设计使用Xilinx的XDMA方案和非Xilinx的RIFFA方案;可将采集的SDI视频通过PCIE高速接口传输到PC,并在PC端通过QT上位机显示图像,反过来,也可以通过PC端的QT上位机采集PC的图像传到FPGA并通过SDI发送,在军工领域应用广泛;该方案目前还在调试中,敬请期待本博推出。。。

4、Xilinx Zynq UltraScale+系列FPGA 方案

Xilinx Zynq UltraScale+系列FPGA拥有成熟的SDI逻辑编解码方案,该方案的核心是采用Xilinx官方的UltraScale GTH+SMPTE UHD-SDI IP核架构,其中,UltraScale GTH负责SDI视频的高速差分信号与并行信号的转换,本博称之为解串与串化;SMPTE UHD-SDI负责并行的SDI视频与BT1120视频的转换;相应的,Xilinx官方也给出了硬件电路参考设计,包括差分时钟设计、驱动器与均衡器设计等;该方案也可以在Kintex UltraScale、Kintex UltraScale+、Vrtix UltraScale、Vrtix UltraScale+系列FPGA上用;

本博不是做硬件电路的,只会看看原理图和芯片手册,更多的还是做Xilinx Kintex7系列FPGA的SDI视频编解码开发应用;基于上述原理,XilinxZynq UltraScale+系列FPGA可实现SDI图像采集传输板卡、可实现SDI工业相机、可实现SDI综合图像处理板卡等项目;有此类项目需求的朋友,推荐本博现有的Xilinx Zynq UltraScale+系列FPGA的SDI视频编解码开发应用如下:

4.1、Zynq UltraScale+ FPGA的SDI视频编解码低延时输出 设计方案

该项目采用Xilinx Zynq UltraScale+ FPGA为平台,采用UltraScale GTH+SMPTE UHD-SDI IP核架构接收3G-SDI视频,经过FIFO缓存后通过SDI视频输出,该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

4.2、Zynq UltraScale+ FPGA的SDI视频编解码缓存输出 设计方案

该方案在4.1章节《Zynq UltraScale+ FPGA的SDI视频编解码 设计方案》的基础上加了将FIFO缓存替换为FDMA缓存,该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

4.3、Zynq UltraScale+ FPGA的SDI视频转DP输出 设计方案

该方案在4.2章节《Zynq UltraScale+ FPGA的SDI视频编解码缓存输出 设计方案》的基础上将SDI输出改为DP输出,该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往

4.4、Zynq UltraScale+ FPGA的SDI视频+GTH高速接口传输 设计方案

该方案在4.2章节《Zynq UltraScale+ FPGA的SDI视频编解码缓存输出 设计方案》的基础上将SDI输出改为GTH高速接口传输,该方案提供2套vivado2019.1版本的工程源码,设计原理框图如下:

关于该方案的详细设计说明,请参考我之前的博客,博客地址如下:

点击直接前往文章来源:https://www.toymoban.com/news/detail-851086.html

5、SDI视频编解码–>项目合作

有SDI视频编解码项目需求的朋友,可以与本博合作开发你需要的项目。。。

我这里有成熟的工程源码,也有对应的FPGA开发板,可提供原型验证项目开发,在此基础上可以提供量产型硬件电路方案+工程源码方案。。。文章来源地址https://www.toymoban.com/news/detail-851086.html

到了这里,关于好物分享:FPGA实现SDI视频编解码的方案设计汇总的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!