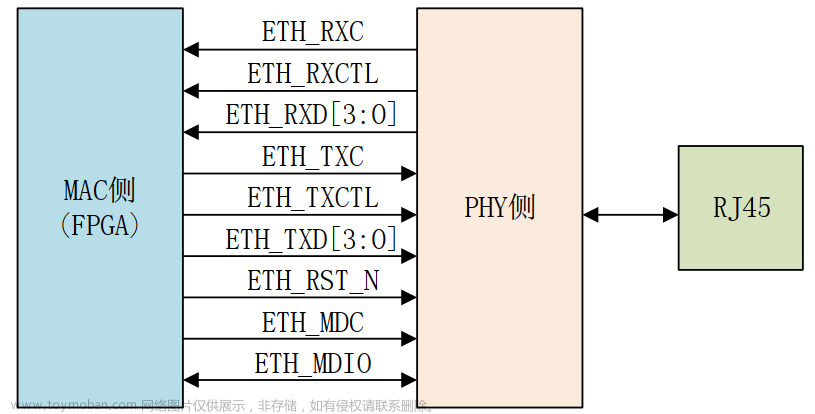

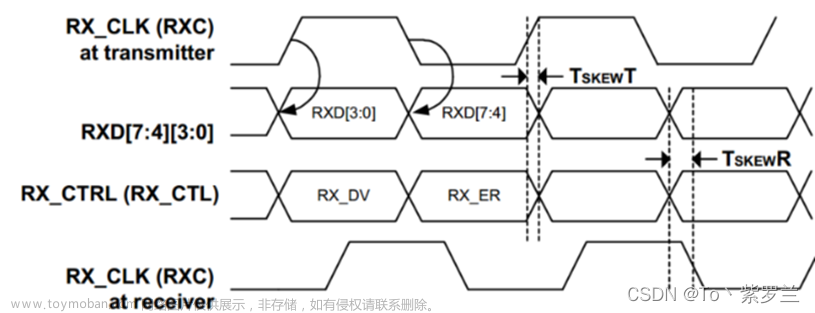

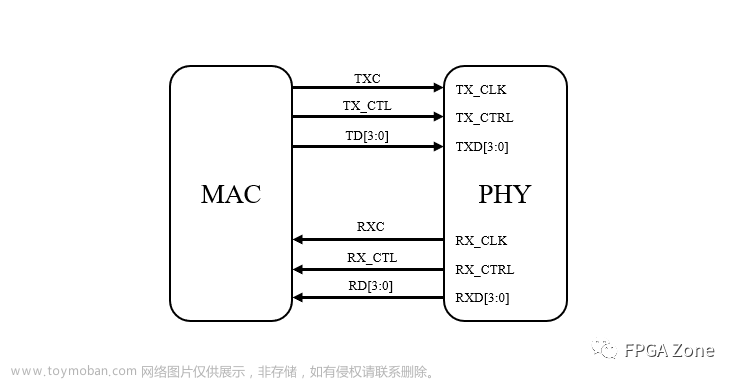

首先需要了解以太网的一些接口协议标准,常见的MII、GMII、RGMII时序,便于后续开发。

【必读】从MII到RGMII,一文了解以太网PHY芯片不同传输接口信号时序!

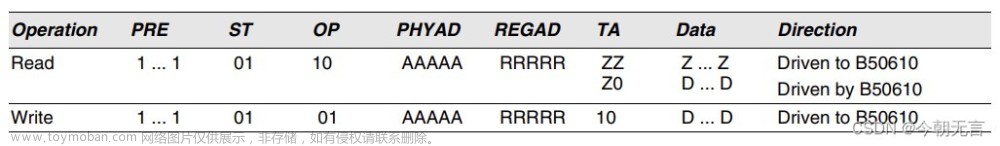

介绍一款比较老的以太网PHY芯片88E1518,具有RGMII接口,分析该芯片的原理图和内部寄存器的配置方式,以及MDIO的时序。

揭秘88E1518以太网芯片:比RTL8211更麻烦,配置多一步”

PC端通过串口调试助手对88E1518内部寄存器进行配置,涉及到uart收发数据模块和MDIO读写时序,用户可以根据定义的串口格式,通过串口助手向88E1518中寄存器写入数据或者读出数据。

“FPGA+MDIO总线+UART串口=高效读写PHY芯片寄存器!“(含源代码)

上面几篇文章是对PHY芯片和协议的相关讲解,下面文章开始对PHY芯片的数据传输接口和讲解、实现以太网协议。

首先需要把88E1518的RGMII双沿采样数据的接口协议转换为单沿传输数据的GMII接口协议,会使用到BUFIO、BUFG、IDDR、ODDR、IDELAYE等原语知识。

基于FPGA的GMII与RGMII接口相互转换(包含源工程文件)

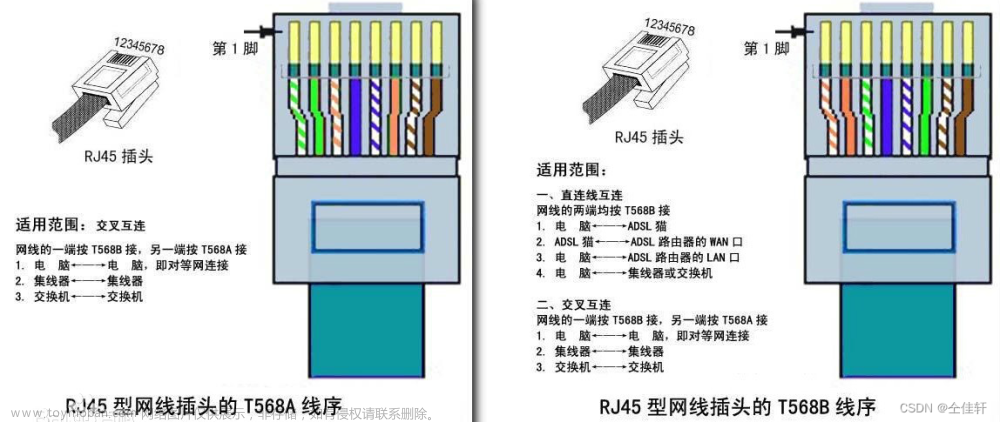

下文讲解以太网帧格式和ARP协议,ARP协议是源主机知道目的主机IP,不知道目的主机物理地址时发起的协议,具体知识可以查看下文。

以太网帧格式及ARP协议简介

上文讲解了ARP以及以太网帧格式,下文通过FPGA实现ARP协议,包括CRC校验,以太网发送和以太网接收等模块。最后通过仿真和上板测试,用户需要掌握PC端清除ARP绑定和发起ARP请求的指令,并且需要简单掌握wireshark的使用。

【实战干货】FPGA实现ARP协议,细节全解析!(包含源工程文件)

下文讲解IP协议和ICMP协议的相关知识,ICMP主要用于检测以太网链路的畅通,回显应答发送的数据与回显请求数据段的数据必须保持一致。

IP协议及ICMP协议简介

通过FPGA实现ICMP协议,用于外设测试以太网链路的畅通,该设计会包含arp协议,用户就不需要手动绑定IP和物理地址,会更加方便。

PC在发送回显请求之前,会发送arp请求获取目的主机的物理地址,可以通过wireshark抓取对应报文。

基于FPGA实现ICMP协议(包含源工程文件)

ARP协议用于获取目的主机的物理地址,ICMP用于测试以太网链路的连接状态,而UDP用于传输数据。

下文简要讲解UDP协议,然后通过FPGA实现该协议,注意本文只是用于熟悉UDP协议的一些知识,对数据做了简要回环,可能会存在一些bug。

对于这个bug我并没有修复,原因在于这个设计中ARP、ICMP、UDP分别通过不同模块实现,这样的设计便于调试或者屏蔽某种协议,但是会消耗更多资源,因此后面会对这三个模块进行整合,合并为一个模块,解决上述问题。

基于FPGA的UDP实现(包含源工程文件)

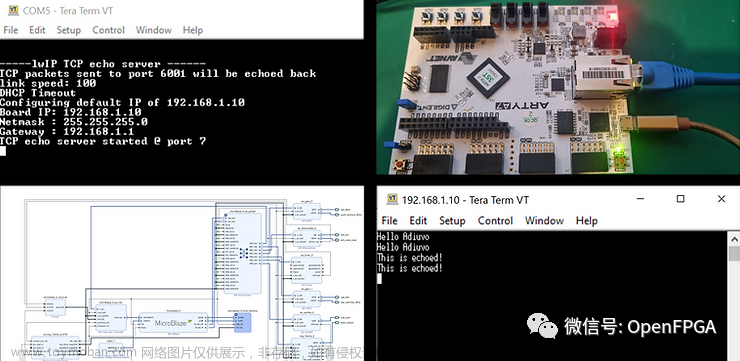

下文就是整合ARP、ICMP、UDP协议的结果,相比前文的工程会节省很多资源,并且加入了帧间隔等信息,修复了发现的bug。上板实测最大发送速率可以达到980Mbps。后续文章使用的以太网UDP模块均是该模块。

基于FPGA的实用UDP设计(包含源工程文件)

下文是以太网模块存在问题的优化,对应工程也已经上传到百度网盘的以太网UDP版本1。

以太网模块问题及优化

上位机通过UDP协议向FPGA传输图像数据,FPGA使用上述设计的模块接收上位机的数据,并且将数据传输给DDR3存储,最后在HDMI显示器上进行显示。下面两篇文章的效果都一样,区别在于mig IP的用户接口不同。

基于FPGA的以太网传输图片通过HDMI显示(含源码)

将Xilinx DDR3 MIG IP核的AXI_FULL接口封装成FIFO接口(含源码)

这篇文章是对前一篇文章中出现的一个bug总结,通过实际现象推测可能出现的原因,然后利用ILA和wireshark抓取关键信号去判断猜想是否正确,最后找到根本原因,解决问题。

以太网传输图片工程出现的问题总结(含源码)

上一篇文章主要用于UDP接收数据报文,下文主要用于测试UDP发送数据报文,OV7725摄像头采集数据,通过FIFO暂存,然后直接通过以太网发送模块将数据发送给PC端,PC端通过上位机显示摄像头的图像信息。

基于FPGA的OV7725网络摄像头(含源码)

设计其实有时候挺烦的,自己的设计出现问题,就只能自己通过ILA这些工具去定位问题,原因在于短时间其他人也不知道你的代码是如何写的,更不知道这个代码中的关键信号,无法帮你定位问题。

因此在设计的时候我通常会将所有模块实现一遍,即便不能替换他人模块,也需要知道他的设计思路,关键信号是哪些,出现问题后如何定位等等。能不能找到更加简便的实现方式,优化一些设计,便于后续替代等等。

只有当你自己能够设计出功能相同甚至功能更优的电路的时候,才是真正掌握了知识,不是把别人代码拿过来用就行了。

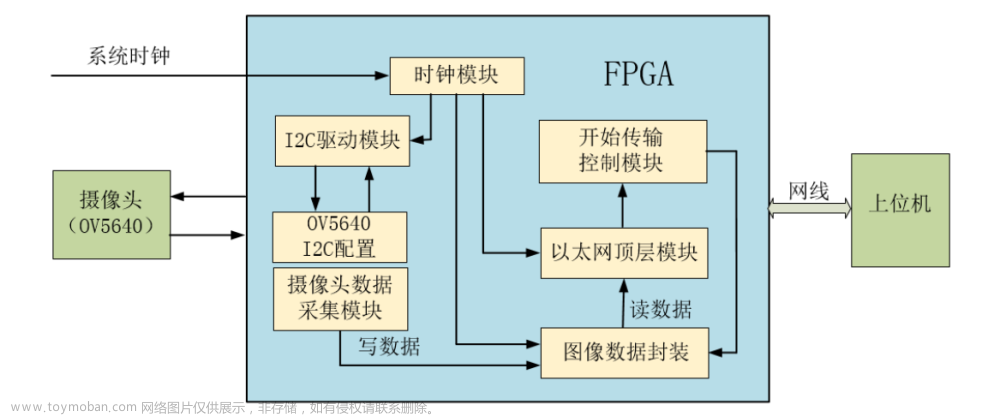

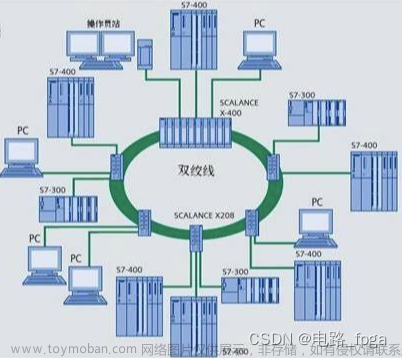

下图用于封面!!!!

如果对文章内容理解有疑惑或者对代码不理解,可以在评论区或者后台留言,看到后均会回复!文章来源:https://www.toymoban.com/news/detail-851122.html

如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!您的支持是我更新的最大动力!将持续更新工程!文章来源地址https://www.toymoban.com/news/detail-851122.html

到了这里,关于基于FPGA的以太网相关文章导航的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!