背景介绍

NVMe协议固态硬盘的速度随所使用的PCIe协议不同而不同。NVMe固态硬盘在PCIe Gen2、Gen3、Gen4条件下,理论有效带宽分别为2GB/s、3.938GB/s、7.877GB/s。目前,基于PCIe Gen5的NVMe SSD在2023年已发布,其理论有效带宽为17.754GB/s。

在之前的帖子中,我们介绍了一个在PCIe3.0协议下的基于FPGA PL的纯逻辑NVMe Host IP(FPGA实现高带宽NVMeSSD读写——纯逻辑实现-CSDN博客),速度可以达到3GB/s,并进一步将其拓展至双路NVMe从而使系统可以同时对两个NVMe硬盘进行读写,速度达到了6GB/s。基于FPGA的技术框架中,AMD(Xilinx)公司只有在其最高端的UltraScale+世代中的Virtex系列的高端器件才提供PCIe 4.0协议的PHY,对应的开发板为型号为VCU128。囿于缺少该板卡,我们还没法进行基于PCIe4.0的NVMe IP的速度测试。

NVMe IP最早的版本是2021年6月发布的基于FPGA Zynq 系列中的PS资源而建的系统(FPGA实现高带宽NVMe SSD读写_fpga nvme ssd-CSDN博客)。在这期间,有不少业界朋友和我们联系,咨询不需要特别高速度的应用中,基于PCIe 2.0和PCIe 1.0协议的NVMe IP性能如何。理论上高版本适配的情况下跑低速协议是适配的,但是没有人会在高性能平台上去做低速的实现,浪费平台性能。本着求实探真的原则,本文中我们对IP进行了适度调整,测试了NVMe IP在PCIe2.0和PCIe1.0协议下的性能。所以本文的测试结果可以客观的反映NVMe IP在Xilinx早期的低速平台上的实际性能。

本NVMe IP的系统框架在之前的帖子中已经介绍过,本篇不再赘述,有兴趣的朋友可以通过我的全部帖子列表(https://blog.csdn.net/weixin_42166371?type=blog)翻看前文。

测试方案

本文的测试内容主要为NVMe IP在PCIe2.0和PCIe1.0协议下的性能,因此选用的主要测试平台是与协议适配的对应Xilinx ZC706,VC707开发板以及FMC接口的NVMe扩展子卡。同时测试高性能平台ZCU106(PCIe 3.0)上IP降速到PCIe 2.0的性能以作为对比。

测试方法与之前的测试相似,使用1000GB的数据,实时测试每个1GB数据的读写性能。

测试平台

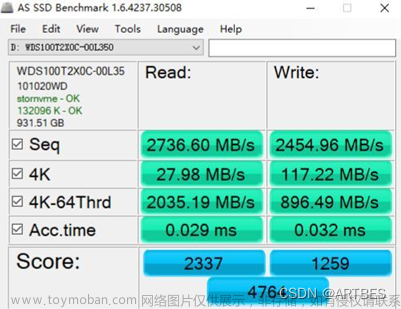

系统的开发及测试都是基于Xilinx官方开发板和FMC NVMe SSD转接卡组成。开发板包括ZCU106,ZC706,VC707,其中ZCU106是我们之前使用调试的板子,其支持2路PCIe 3.0,而ZC706和VC707均不支持PCIe 3.0,ZC706支持2路PCIe 2.0,VC707只支持1路PCIe 2.0。根据之前的测试结果,本次实验选用较为稳定性能较好的三星980Pro,同时也是为了验证在较低速度下980Pro的速度是否还会再次变化。

测试结果

单路NVMe测试

VC707和ZC706平台下测得的读写盘速度都是相近的。从图中可以看出,在PCIe2.0下,单盘的读盘速度约为1.4GB/s,写盘速度则是约为1.2GB/s。三星980Pro的写盘速度没有像PCIe 3.0下的速度跌落,始终保持较为稳定的速度。NVMe协议的固态硬盘在PCIe Gen2 4x理论有效带宽为2GB/s,而我们NVMe IP最高速度达到了1.4GB/s,达到了理论带宽的70%。由于协议中存在物理层编码开销、Packet Non-Payload 开销、TLP 间隔开销以及ACK 与流控开销,我们认为70%的效率已经是一个比较高的数值了。

同样我们用VC707和ZC706平台进行了PCIe 1.0的测试,VC707和ZC706的读盘速度均约为820MB/s,写盘速度均约为780MB/s。NVMe协议的固态硬盘在PCIe Gen1 4x理论有效带宽为1GB/s,读盘的有效带宽已达到了理论带宽的82%,这个数据让人十分惊喜。

双路NVMe测试

根据Xilinx的官方手册,VC707只支持一路PCIe 2.0链接,ZC706支持两路PCIe2.0链接,因此我们只使用了ZC706进行双路NVMe测试。

ZC706平台下的双路PCIe2.0 NVMe系统读写盘速度如图所示。从图中可以看出,双盘的读盘速度约为2.0GB/s,写盘速度则是约为1.8GB/s,这个速度与预期不符(读盘期望值为2.8GB/s左右)。经过一系列测试及查证,发现虽然我们设置的是两路PCIe 2.0,但系统将其自动配置为一路PCIe 2.0和一路PCIe 1.0,总的速度也与两种协议下单路PCIe的速度叠加接近,我们认为这可能是PCIe PHY IP的问题。

高速平台PCIe2.0测试

ZC706平台下的双路PCIe2.0 NVMe测试的意外结果给了我们带来一个疑问,如果使用ZCU106,用其支持的两路PCIe 3.0,对其进行降速到PCIe 2.0,运行出来的结果是什么样子?会不会也出现类似的协议变化的现象?为此我们使用ZCU106分别进行单路PCIe2.0 NVMe和双路PCIe2.0 NVMe的测试。为了简化测试,我们仅进行了PCIe2.0 NVMe读数据的性能测试。

单路NVMe测试中,读盘的速度达到了1.5GB/s,这个速度比基于VC707/ZC706平台的1.4GB/s要快一些;在双路NVMe测速中,读盘的速度达到了2.9GB/s,没有出现协议降档的情况(一路PCIe2.0,一路PCIe1.0)。

对于ZCU106平台的PCIe2.0 NVMe速度快于VC707/ZC706平台的PCIe2.0 NVMe,我们认为主要有两个原因,第一是ZCU106系统使用的硬件与VC707/ZC706有一定差异。例如在ZCU106的板子上使用的DDR4,其时钟是300MHz,而在VC707/ZC706上使用的是DDR3,其时钟是200MHz,这使得IP在与DDR传输时的速度不同;第二,由于PCIe 3.0相较于PCIe 2.0已经有一定的协议更新,物理通路相较于传统PCIe 2.0已经有一定提升,因此在支持PCIe3.0的ZCU106上跑PCIe 2.0的速度会比只支持PCIe 2.0的两个板子速度略快。

结语

我们设计的FPGA纯逻辑实现的高带宽NVMe SSD读写的IP同样可以适用于PCIe 2.0和PCIe 1.0的协议标准,其速度可达1.4GB/s及820MB/s,且效率分别达到了70%和83%,这已经比较接近Xilinx平台的最大速度,这同时也证明了我们的IP的适用性。最后的测试结果也表明,我们最初的考虑是有道理的。将高版本的IP在低速协议上可以适配,但是不一定是低速协议实际的速度。

如果需要讨论,联系方式如下:

地址:北京市海淀区中关村南大街5号北京理工大学。

电话:13810602873(微信同号)

E-mail:liuzhenyu@bit.edu.cn文章来源:https://www.toymoban.com/news/detail-851275.html

声明

在本文的结尾,我们做如下声明:本次的测试仅仅是作为与该领域感兴趣的朋友交流之用。由于测试环境受限,有的硬盘的速度可能并没有达到该盘的最大值,测试结果仅代表我们在此次实验中的测试结果,不代表盘的最优性能。我们仅对某款型号的某块盘,基于FPGA平台,用自己的测试程序做了统一的、无差别的测试而得到了结果。我们仅对我们的方法及所用的盘负责,保证不出现虚假或是伪造的结果。但不是对市场上所有的该型号或类似的产品性能做出推断或推论。本文的数据发布出来,仅供大家参考。文章来源地址https://www.toymoban.com/news/detail-851275.html

到了这里,关于FPGA实现的PCIe2.0与PCIe1.0 NVMe IP性能测试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!