0 工具准备

1.野火 stm32f407霸天虎开发板

2.LAN8720数据手册

3.STM32F4xx中文参考手册

1 PHY(LAN8720)硬件配置

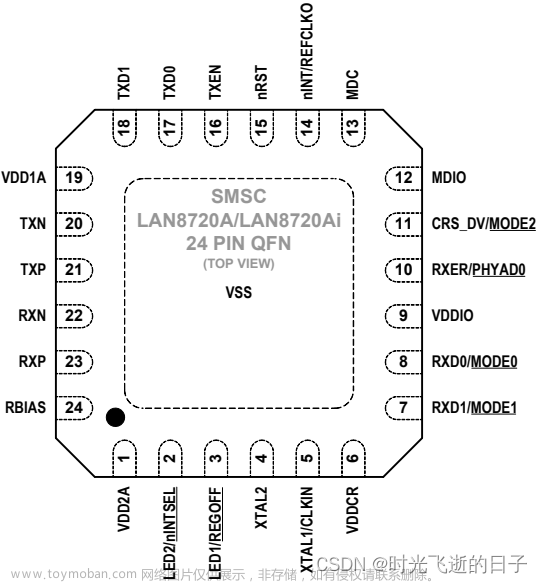

1.1 硬件配置引脚说明

在LAN8720上电或复位时会读取一些特定引脚的电平,根据电平来进行硬件配置。LAN8720的引脚分布如下:

注意,LAN8720有些引脚内部自带上/下拉,定义如下:

1.1.1 PHY地址配置

LAN8720的PHYAD[0]用来配置PHY地址的bit0,当接入了多个PHY时可以用来区分不同的PHY。该引脚自带内部下拉,同时我们也只用到了一片LAN8720,因此悬空即可。

1.1.2 模式配置

这里的模式指的是传输速度(10Mbps/100Mbps)以及全/半双工,通常我们将MODE引脚都设置为1,MODE引脚内部自带上拉,因此MODE[2:0]引脚无需外加上拉电阻。也就是让LAN8720启用自动协商,它会自动寻找最优的工作方式。关于模式配置引脚说明如下:

MODE[2:0]是复用引脚,复用功能如下:

1.1.3 1.2V内部电压源配置

REGOFF引脚决定LAN8720选择外部还是内部1.2V电源,内部自带下拉电阻。当输入电平为低时选择内部1.2V电源,当输入电平为高时选择外部1.2V电源。这里我们选择内部1.2V电源,无需外加下拉电阻。

1.1.4 nINT/REFCLKO配置

当nINTSEL引脚电平为低时nINT/REFCLKO被设置为50MHz时钟输出,当nINTSEL引脚电平为高时nINT/REFCLKO被设置为中断信号输出(低电平有效)。该引脚内部自带上拉,我们通常使用LAN8720提供50MHz时钟,因此该引脚需要外部下拉。 文章来源:https://www.toymoban.com/news/detail-851413.html

文章来源:https://www.toymoban.com/news/detail-851413.html

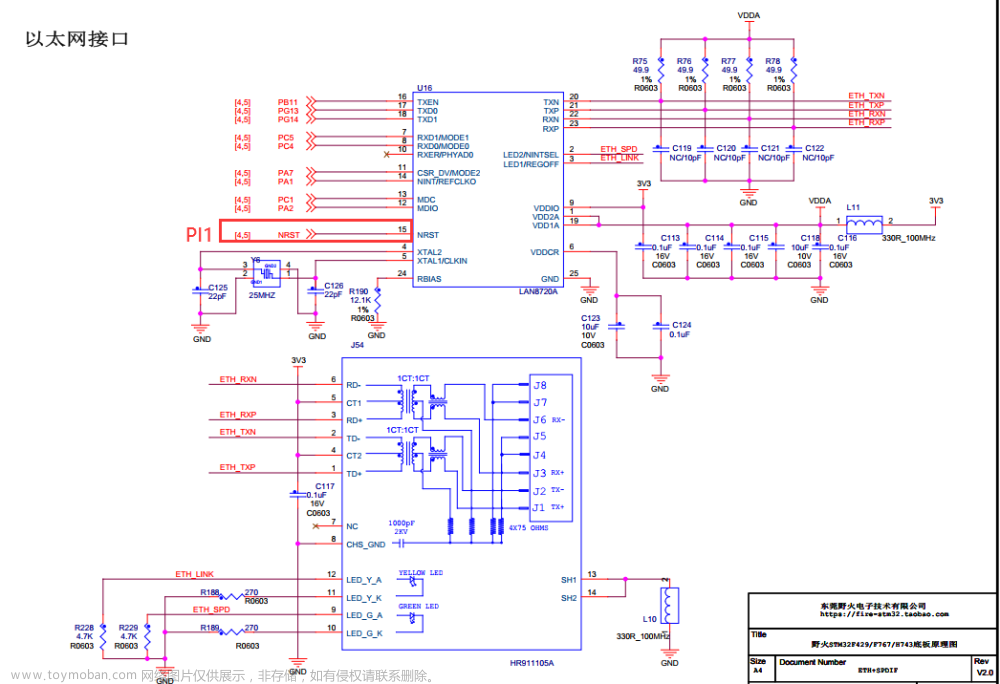

2 PHY(LAN8720)和MCU连接

由于LAN8720仅支持RMII和SMI接口,因此PHY和MCU的连接就通过RMII和SMI接口实现。原理图设计如下:

这里将REGOFF和nINTSEL引脚下拉,也就是使用内部1.2V电源、REF_CLK输出50MHz时钟。RMII和SMI接口连线按照标准进行连接即可。文章来源地址https://www.toymoban.com/news/detail-851413.html

到了这里,关于STM32的以太网外设+PHY(LAN8720)使用详解(2):硬件设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!