概述

LS1043A处理器是推出的第一款面向嵌入式网络的四核64位Arm®处理器。LS1043A (四核版本)可通过支持无风扇设计的灵活I/O封装,提供超过10 Gbps的性能。这款SoC是专为小规格网络、工业和汽车应用而打造的解决方案,针对经济型低端PCB优化了物料成本(BOM),降低了电源成本,采用单时钟设计。

全新0.9V版LS1043A能够为无线LAN和以太网供电系统进一步降低能耗。全新的23x23封装方式,支持引脚兼容设计,可扩展至LS1046A (四核A72处理器)或LS1088A (十核A53处理器)。

LS1043A能够提升双核32位Arm 产品的性能,并且延续了QorIQ系列一贯的I/O灵活性,集成了QUICC Engine®,继续提供对HDLC、TDM或Profibus的无缝支持。

器件

LS1043AXE7PQB

产品种类:微处理器 - MPU

核心:ARM Cortex A53

内核数量:4 Core

数据总线宽度:64 bit

最大时钟频率:1.4 GHz

封装 / 箱体:FC-PBGA-621

L1缓存指令存储器:32 kB

L1缓存数据存储器:32 kB

工作电源电压:1 V

系列:LS1043A

安装风格:SMD/SMT

工作温度:-40°C ~ 105°C

资格:AEC-Q100

数据 RAM 大小:128 kB

接口类型:Ethernet, I2C, PCI-e, Serial, USB

L2缓存指令/数据存储器:1 MB

存储类型:DDR3L / DDR4 SDRAM

计时器/计数器数量:8 Timer

处理器系列:四核 Layerscape LS1043A

看门狗计时器:Watchdog Timer

单位重量:2.112 g

LS1043AXE8MQB

核心:ARM Cortex A53

内核数量:4 Core

数据总线宽度:64 bit

最大时钟频率:1.2 GHz

封装 / 箱体:FC-PBGA-780

L1缓存指令存储器:32 kB

L1缓存数据存储器:32 kB

工作电源电压:1 V

系列:LS1043A

安装风格:SMD/SMT

工作温度:-40°C ~ 105°C

资格:AEC-Q100

数据 RAM 大小:128 kB

接口类型:Ethernet, I2C, PCI-e, Serial, USB

L2缓存指令/数据存储器:1 MB

存储类型:DDR3L / DDR4 SDRAM

计时器/计数器数量:8 Timer

处理器系列:四核 Layerscape LS1043A

看门狗计时器:Watchdog Timer

单位重量:1.469 g

LS1043AXE8PQB

产品种类:微处理器 - MPU

核心:ARM Cortex A53

内核数量:4 Core

数据总线宽度:64 bit

最大时钟频率:1.4 GHz

封装 / 箱体:FC-PBGA-780

L1缓存指令存储器:32 kB

L1缓存数据存储器:32 kB

工作电源电压:1 V

系列:LS1043A

安装风格:SMD/SMT

工作温度:-40°C ~ 105°C

数据 RAM 大小:128 kB

接口类型:Ethernet, I2C, PCI-e, Serial, USB

L2缓存指令/数据存储器:1 MB

存储类型:DDR3L / DDR4 SDRAM

计时器/计数器数量:8 Timer

处理器系列:四核 Layerscape LS1043A

看门狗计时器:Watchdog Timer

单位重量:1.469 g

LS1043AXE8QQA

产品种类:微处理器 - MPU

核心:ARM Cortex A53

内核数量:4 Core

数据总线宽度:64 bit

最大时钟频率:1.6GHz

封装 / 箱体:PBGA-780

L1缓存指令存储器:32 kB

L1缓存数据存储器:32 kB

系列:LS1043A

安装风格:SMD/SMT

最大工作温度:+105°C

数据 RAM 大小:128 kB

接口类型:Ethernet, I2C, SPI, UART, USB

L2缓存指令/数据存储器:1 MB

存储类型:DDR3L, DDR4

Layerscape® 1043A处理器:LS1043AXE7PQB、LS1043AXE8MQB、LS1043AXE8PQB、LS1043AXE8QQA面向嵌入式网络应用的64位Arm®处理器 —— 明佳达

特性

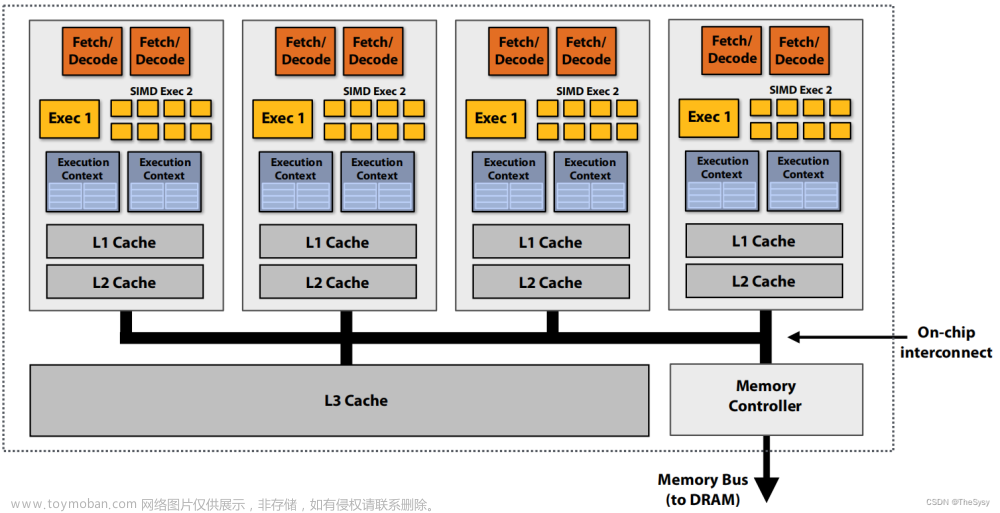

- 四核(LS1043A)或双核(LS1023A) Arm® Cortex®-A53 64位内核

- 1 GHz至1.6 GHz

- 32/32 I/D缓存KB L1和1 MB L2缓存

网络元件

- 多达7个1x GbE或1x 10GbE和5个1x GbE

- 四通道SerDes,高达10 GHz,控制器间多路复用,支持:

- 3个第二代PCI Express®接口

- SATA 3.0接口

- uQUICC Engine

加速器和存储器控制

- DPAA解析、分类和分发引擎

- 内置安全引擎

- DDR 3L/4

基本外设和互连

- 3个带PHY的USB 3.0接口

- QuadSPI

- IFC闪存

- 四通道I²C

- 信任区

其他特性

- QorIQ平台可信架构

- 面向硬件增强虚拟化的Arm SMMU

- 面向超低功耗设计的0.9V选项

- 23x23封装方式,支持引脚兼容和性能扩展

应用

消费电子产品

无线/远程信息处理安全网关

工业

工业网关

网络

分支路由器

家庭网关

集成服务网关

IP-PBX

vCPE/uCPE

无线LAN (WLAN) 接入点文章来源:https://www.toymoban.com/news/detail-851943.html

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!文章来源地址https://www.toymoban.com/news/detail-851943.html

到了这里,关于Layerscape® 1043A处理器:LS1043AXE7PQB、LS1043AXE8MQB、LS1043AXE8PQB、LS1043AXE8QQA面向嵌入式网络应用的64位Arm®处理器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!