1.背景介绍

密码学算法在现代加密技术中扮演着至关重要的角色。随着数据量的增加,密码学算法的性能成为了关键因素。因此,加密算法的加速成为了研究的热点。FPGA(可编程门 arrays)是一种高性能、可定制的硬件加速技术,它具有高度并行性和低延迟,使其成为加速密码学算法的理想选择。本文将讨论 FPGA 加速密码学算法的关键技术,包括算法优化、硬件平台优化、并行处理和流水线处理等方面。

2.核心概念与联系

2.1 FPGA 基本概念

FPGA 是一种可编程电路板,由多个可配置的逻辑门组成。它可以根据需要进行配置和优化,以满足不同的应用需求。FPGA 具有以下特点:

- 可配置性:FPGA 可以根据用户需求进行配置,实现各种不同的逻辑门和电路。

- 高性能:FPGA 具有高度并行性和低延迟,可以实现高性能计算。

- 可扩展性:FPGA 可以通过扩展设备和内存来满足不同的需求。

2.2 密码学算法基本概念

密码学算法是一种用于保护数据和通信的方法,主要包括加密和解密过程。密码学算法可以分为对称密码和非对称密码两类。对称密码使用相同的密钥进行加密和解密,如AES、DES等;非对称密码使用不同的公钥和私钥进行加密和解密,如RSA、ECC等。

3.核心算法原理和具体操作步骤以及数学模型公式详细讲解

3.1 AES加速

AES(Advanced Encryption Standard,高级加密标准)是一种对称密码算法,被广泛应用于加密通信和保护数据。AES的核心操作包括:

- 加密:将明文加密成密文。

- 解密:将密文解密成明文。

AES的主要步骤如下:

- 加载密钥:将密钥加载到AES算法中。

- 初始化状态:将明文分为128位(AES-128)、192位(AES-192)或256位(AES-256)的状态数组。

- 10个轮循环:对状态数组进行10次轮循环处理,每次循环包括以下步骤:

- 加密:使用轮键和状态数组中的每个字节进行加密。

- 混淆:对加密后的状态数组进行混淆操作。

- 替换:对混淆后的状态数组进行替换操作。

- 解密:将密文解密成明文。

AES的数学模型公式如下:

$$ F(x) = x \oplus (x \ll 1) \oplus (x \ll 2) \oplus (x \ll 3) $$

其中,$\oplus$ 表示异或运算,$\ll$ 表示左移运算。

3.2 RSA加速

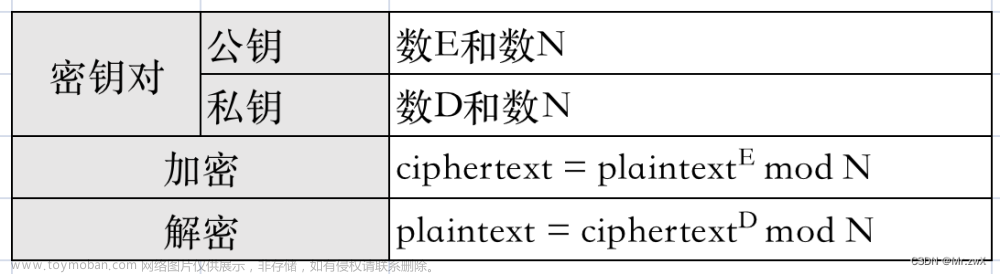

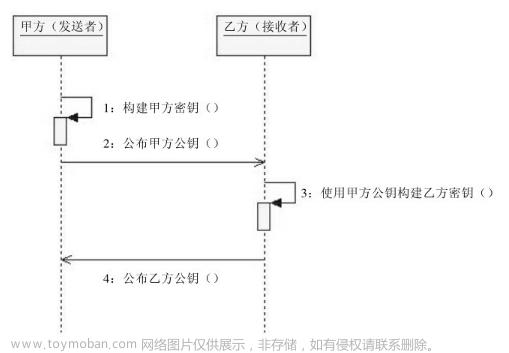

RSA(Rivest-Shamir-Adleman)是一种非对称密码算法,被广泛应用于数字签名和密钥交换。RSA的核心操作包括:

- 加密:将明文加密成密文。

- 解密:将密文解密成明文。

RSA的主要步骤如下:

- 生成公钥和私钥:生成一个大素数p,然后计算q,n=pq。选择一个大素数e(e和pq互质),计算d(d和e互质)。公钥为(n,e),私钥为(n,d)。

- 加密:将明文m加密成密文c,使用公钥(n,e)。

- 解密:将密文c解密成明文m,使用私钥(n,d)。

RSA的数学模型公式如下:

$$ c = m^e \bmod n $$

$$ m = c^d \bmod n $$

其中,$m$ 表示明文,$c$ 表示密文,$n$ 表示公钥,$e$ 表示加密公钥,$d$ 表示解密私钥。

4.具体代码实例和详细解释说明

4.1 AES加速代码实例

以下是一个使用FPGA加速AES算法的代码实例:

```c

include

include "aes.h"

int main() { unsigned char key[16]; unsigned char plaintext[16]; unsigned char ciphertext[16];

// 初始化AES算法

aes_init();

// 设置密钥

for (int i = 0; i < 16; i++) {

key[i] = i;

}

// 设置明文

for (int i = 0; i < 16; i++) {

plaintext[i] = i;

}

// 加密

aes_encrypt(key, plaintext, ciphertext);

// 解密

aes_decrypt(key, ciphertext, plaintext);

return 0;} ```

4.2 RSA加速代码实例

以下是一个使用FPGA加速RSA算法的代码实例:

```c

include

include "rsa.h"

int main() { unsigned int p, q, n, phi, e, d; unsigned int m, c;

// 生成大素数

p = rand() % 1000000000 + 1;

q = rand() % 1000000000 + 1;

// 计算n和phi

n = p * q;

phi = (p - 1) * (q - 1);

// 选择大素数e和d

e = rand() % phi + 1;

d = inverse(e, phi);

// 生成公钥和私钥

unsigned int public_key[2] = {n, e};

unsigned int private_key[2] = {n, d};

// 加密

m = rand() % 1000000000 + 1;

c = rsa_encrypt(m, public_key);

// 解密

m = rsa_decrypt(c, private_key);

return 0;} ```

5.未来发展趋势与挑战

未来,FPGA加速密码学算法将面临以下挑战:

- 算法优化:密码学算法的优化将成为关键技术,以提高算法的性能和效率。

- 硬件平台优化:将密码学算法移植到不同的硬件平台,以满足不同的应用需求。

- 并行处理:利用FPGA的高度并行性,进一步优化密码学算法的并行处理。

- 流水线处理:将密码学算法的不同步骤进行流水线处理,以提高算法的执行效率。

- 安全性:密码学算法的安全性将成为关键问题,需要不断更新和优化算法,以应对新的安全威胁。

6.附录常见问题与解答

Q:FPGA加速密码学算法与传统加速方法有什么区别?

A:FPGA加速密码学算法与传统加速方法(如CPU、GPU等)的主要区别在于硬件平台和并行处理能力。FPGA具有高度可定制化和高度并行性,可以根据需求进行配置和优化,实现高性能计算。而传统加速方法如CPU和GPU主要面向通用计算,性能和定制度有限。

Q:FPGA加速密码学算法的应用场景有哪些?

A:FPGA加速密码学算法的应用场景包括但不限于:

- 加密通信:提高加密和解密过程的性能,保证数据的安全传输。

- 密钥管理:实现高性能的密钥生成、存储和管理。

- 数字签名:提高数字签名的生成和验证速度,保证数据的完整性和来源认证。

- 密码分析:实现高性能的密码分析算法,用于恶意软件检测和网络安全监控。

Q:FPGA加速密码学算法的优缺点有哪些?

A:FPGA加速密码学算法的优缺点如下:

优点:文章来源:https://www.toymoban.com/news/detail-852905.html

- 高性能:FPGA具有高度并行性和低延迟,可以实现高性能计算。

- 可定制化:FPGA可以根据需求进行配置和优化,实现特定的加密算法优化。

- 低功耗:FPGA可以实现高性能计算而保持低功耗,适用于移动设备和绿色计算。

缺点:文章来源地址https://www.toymoban.com/news/detail-852905.html

- 开发成本:FPGA开发需要专业的硬件知识和技能,开发成本较高。

- 生产成本:FPGA生产需要专业的制造设备和技术,生产成本较高。

- 可靠性:FPGA的可靠性可能较低,需要进行充分的测试和验证。

到了这里,关于FPGA加速:提高密码学算法性能的关键技术的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!