一、查看灰度图的数据格式

1.1 安装HxD

HxD下载链接:https://download.csdn.net/download/weixin_44357071/89045331

解压直接打开exe就能使用。

将需要查看二进制数据的图片拖到软件框里就能读取

1.2 找到bmp图像的图片点阵数据起始地址,原理和例子

从000Eh(h是16进制的意思)到0035是真的有40byte.横坐标是零到16,竖坐标是像十进制一样,把个位数空出来,然后是10,20,30.....

图中框框里是一个byte(字节),等于8个bit,A是4位bit的16进制表示,0也是。

如下图例子:

0000h到000Dh是位图文件头

000Eh到0035h是位图信息头,其中的001Ch是调色板颜色种类的位宽,这里是1,两种颜色,一种颜色需要4个字节,所以调色板需要2*4=8字节

所以0036h到003Dh是调色板所占的字节

003Eh及之后都是图片的点阵数据

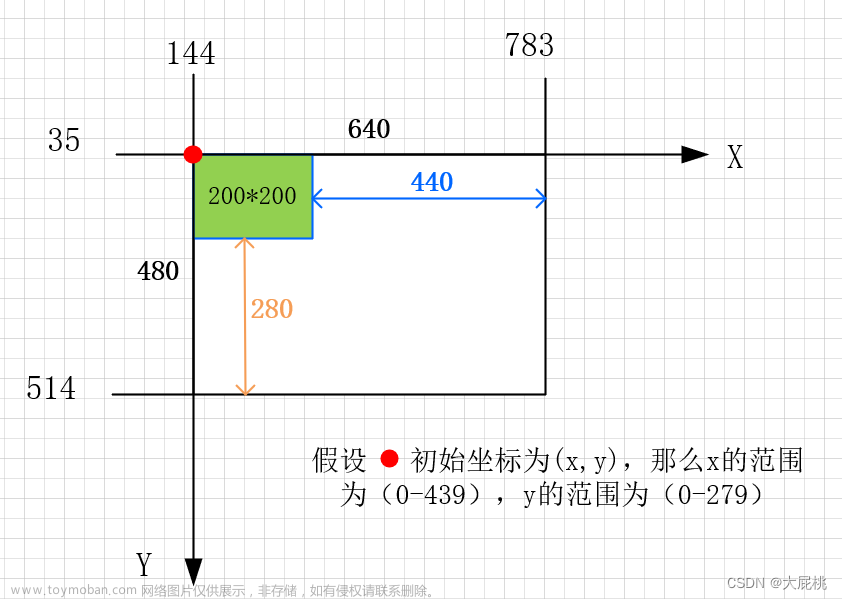

1.3 生成200*200的灰度图

右键点击图片,打开方式选择“画图”

修改尺寸为宽200,高200,即可将原来的800*800灰度图变为200*200,注意,如果颜色不改为黑白,可能会导致后续的verilog代码无法处理。

在画图界面点击另存为 256色的位图

1.4 选择图片的点阵数据

0000h到000Dh是位图文件头

000Eh到0035h是位图信息头,其中的001Ch是调色板颜色种类的位宽,这里是8,256种颜色,一种颜色需要4个字节,所以调色板需要256*4=1024字节

所以0036h到003Dh是调色板所占的字节

003Eh及之后都是图片的点阵数据

二、 额外学习:对比度代码和注释,代码没跑通,后续尝试解决

需要注意$fopen等函数的使用,要打开的文件应该放在vivado的哪个目录下。链接:

verilog中的testbench语句——display,fopen,fread,fwrite——更新中-CSDN博客

2.1 设计代码

module contrast_adjust

(

input clk,

input rst_n,

input image_process_start,

input [7:0] point_data_in,

input [2:0] mul_value, //range 0~7

output reg [7:0] point_data_out

);

//----------------signal------------------

//线网型,用来传递值给下一个寄存器??

wire [10:0] point_data_temp0;

wire [8:0] point_data_temp1;

wire [7:0] point_data_out_processed;

/*******************image point process**********************/

//-----------multiple------------

//因为乘以的数是在 0到7,所以乘以 2的3次方,temp0就需要在8位的基础上拓展到10

assign point_data_temp0 = point_data_in * mul_value;

//divide 4,这个应该是通过直接取高8位的方法,实现右移两位,除以4

//point_data_temp0[10:2] 是9位,然后通过第九位进行下一步的判断

assign point_data_temp1 = point_data_temp0[10:2];

//----------overflow process-----

//如果取高八位的数最高位依旧是1,即值大于等于100,那么直接给赋值到255,因为除以4了都还大于100

//否则就截取的9位再取低8位,相当于再除以2,因为判断最高位是0了,所以这个右移是无损的

assign point_data_out_processed = point_data_temp1[8]?8'b1111_1111: point_data_temp1[7:0];

always @ (posedge clk or negedge rst_n)

if(!rst_n)

point_data_out <= 0;

else if(image_process_start)

point_data_out <= point_data_out_processed;

else

point_data_out <= point_data_in;

endmodule

2.2 tb代码

`timescale 1ns / 1ns

`define Clock 20

module constrast_adjust_tb();

/**************************port*************************/

reg clk;

reg rst_n;

reg [7:0] point_data_in;

reg [2:0] mul_value;

//reg [7:0] add_value;

reg image_process_start;

reg [7:0] bmp_data[0:50000];

wire [7:0] point_data_out;

wire [7:0] bmp_data_out;

/**************************clock and reset*************************/

//初始化时钟,设置时钟周期为20

initial begin

clk= 1;

forever

#(`Clock/2) clk = ~clk;

end

initial begin

rst_n= 0;

#(`Clock*20+ 1);

rst_n =1;

end

/**************************读取位图数据*************************/

integer bmp_file_read;

integer file_read;

integer data_start_index;

integer bmp_size;

initial begin

//返回值bmp_file_read像是一个fd,文件标识符,在verilog里边习惯叫做句柄

//rb表示read only+ binary,只读+二进制模式

bmp_file_read= $fopen("../pic/picture.bmp","rb");

//这行代码的作用是从之前打开的名为 bmp_file_read 的文件中读取数据,

//并将读取的数据存储到 bmp_data 变量中。

file_read= $fread(bmp_data, bmp_file_read);

//找到位图数据开始的索引

data_start_index= { bmp_data[13], bmp_data[12],bmp_data[11],bmp_data[10]};

//得到bmp图像的大小

bmp_size= { bmp_data[5], bmp_data[4], bmp_data[3], bmp_data[2] };

end

/**************************输入 信号*************************/

initial begin

mul_value= 3'd2;

end

integer index;

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)begin

index <= 0;

image_process_start <= 0;

point_data_in <= 0;

end

else if(index == data_start_index)begin

image_process_start <= 1;

index <= index + 1;

point_data_in <= bmp_data[index];

end

else begin

index <= index + 1;

point_data_in <= bmp_data[index];

end

end

assign bmp_data_out = point_data_out;

//--------------------图像写回文件------------------

integer bmp_file_write;

integer file_write;

initial begin

//创建文件,然后得到句柄bmp_file_write

bmp_file_write = $fopen("../pic/picture_contrast.bmp","wb");

end

//每一次时钟上升沿把数据写回

always @ (posedge clk or negedge rst_n)begin

//好像意思是,不复位的情况下,传输正常进行,不知道对不对????????????????

if(rst_n)begin

if(index == 0 || index == 1)

$display("start to write bmp file");

//一直保持写数据,直到写到bmp文件大小+2,因为0和1不写数据

else if(index < bmp_size + 2)

//不理解这个为什么是%c,为什么不是%b呢???????????????????????????????????????????

//将bmp_data_out的数据写到bmp_file_write这个fd中

$fwrite(bmp_file_write,"%c",bmp_data_out);

else begin

$fclose(bmp_file_write);

$fclose(bmp_file_read);

$display("Write bmp file complete, close the file");

$finish;

end

end

end

contrast_adjust u_contrast_adjust(

.clk ( clk ),

.rst_n ( rst_n ),

.image_process_start ( image_process_start ),

.point_data_in ( point_data_in ),

.mul_value ( mul_value ),

.point_data_out ( point_data_out )

);

endmodule

2.3 报错

读图像应该是已经读到数据了,但是数据的输出没有找到,也更改过图像的显示宽度,有一个warning:

WARNING: [Wavedata 42-489] Can't add object "/constrast_adjust_tb/bmp_data" to the wave window because it has 400008 bits, which exceeds the display limit of 65536 bits. To change the display limit, use the command "set_property display_limit <new limit> [current_wave_config]".

代码的索引那一块没看懂

最后再文件夹里面能显示图像,但是文件是空的,说明读写的文件夹没放错地方,在vivado目录的正确位置,但是数据没有正确的写入。

2.4 报错解决方法

vivado默认的仿真时间不够处理像素点的加和,每一个时钟周期才给输出文件写入一个像素点的数据。

所以延长仿真时间就可以,点击下图1处,几秒之后数据处理完毕再点击2处,停止仿真就可以。

三、亮度调节的代码和注释

某段代码的注释

//以后就默认黑白的256色的图就是这个数据

bmp_width = {bmp_data[21],bmp_data[20],bmp_data[19],bmp_data[18]};

bmp_hight = {bmp_data[25],bmp_data[24],bmp_data[23],bmp_data[22]};

data_start_index = {bmp_data[13],bmp_data[12],bmp_data[11],bmp_data[10]};

bmp_size = {bmp_data[5],bmp_data[4],bmp_data[3],bmp_data[2]};

全部代码

//Created on March 10,2020. 2023-03-26,1s=1000ms=10^6us=10^9ns

// 400x400=160000,T=10ns, set Simulation time 20 0000 0ns=2ms

`timescale 1 ns/1 ns

module image_brightness_adjust_tb;

integer fileId, cc,out_file,i;

reg [7:0] bmp_data [0:500000];

reg [7:0] bmp_data_add [0:500000];

reg clk;

//这个应该是灰度的数据

reg [7:0] data;

integer bmp_width, bmp_hight, data_start_index, bmp_size;

integer temp,index;

//----------------------

initial

begin

//fileId = $fopen("E:\\Class_ex\\modelsim\\read_bmpfile_br_adj\\400x400gray.bmp","rb");

fileId = $fopen(".\\400x400gray.bmp","rb");

//out_file = $fopen("E:\\Class_ex\\modelsim\\read_bmpfile_br_adj\\output_file.bmp","wb");

out_file = $fopen(".\\output_file.bmp","wb");

//这里是将fileID的值,以比特进行索引,写到bmp_data里面

cc = $fread(bmp_data, fileId);

$display("%d",cc);

//以后就默认黑白的256色的图就是这个数据

bmp_width = {bmp_data[21],bmp_data[20],bmp_data[19],bmp_data[18]};

bmp_hight = {bmp_data[25],bmp_data[24],bmp_data[23],bmp_data[22]};

data_start_index = {bmp_data[13],bmp_data[12],bmp_data[11],bmp_data[10]};

bmp_size = {bmp_data[5],bmp_data[4],bmp_data[3],bmp_data[2]};

// copy bmp file's (1)(2)(3) parts

//这是是位图的灰度数据之前的部分,

for(index=0;index<data_start_index;index=index+1)

bmp_data_add[index]=bmp_data[index];

//这个是灰度数据的部分,亮度加30

// pixels add 30

for(index=data_start_index;index<=bmp_size;index=index+1)

begin

temp=bmp_data[index];

//if((bmp_data[index]<245) &(bmp_data[index]>105)) bmp_data_add[index]=bmp_data[index]+10;

//if(bmp_data[index]<8'd200) bmp_data_add[index]=bmp_data[index]+8'd10;

if(temp+8'd30>8'd255) bmp_data_add[index]=8'd255;

else bmp_data_add[index]=bmp_data[index]+8'd30;

end

//write data to file

for(i=0;i<bmp_size;i = i + 1)

begin

@(posedge clk)

$fwrite(out_file,"%c",bmp_data_add[i]);

//%b Binary ; //%h,file size:81KB;%c, 41KB,bmp format

end

$fclose(fileId);

$fclose(out_file);

end

//------------------------------------------------

initial

begin

i=0;

end

//------------------------------

// always@(posedge clk )

// begin

// data<=bmp_data[i];

// // i<=i+1;

// end

//--------------------------------------

initial

begin

clk =1;

forever #5 clk=~clk; // T=10ns,f=100MHz

end

endmodule

四、效果展示文章来源:https://www.toymoban.com/news/detail-853453.html

文章来源地址https://www.toymoban.com/news/detail-853453.html

文章来源地址https://www.toymoban.com/news/detail-853453.html

到了这里,关于视觉信息处理与FPGA实现第八次作业——verilog实现亮度调节的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!