FPGA纯verilog编解码CameraLink视频

本文详细描述了FPGA纯verilog实现CameraLink视频接收和发送的实现设计方案,目的在于验证CameraLink解码模块和编码模块的正确性,思路是这样的,由于项目之处没有CameraLink相机,但又必须验证关键的CameraLink解码模块和编码模块,所以做了这样一个巧妙的设计:

先采集HDMI输入视频,经HDMI解码模块解为RGB数据后送入CameraLink编码模块,出来的就是CameraLink的LVDS差分视频信号了,再把这个信号通过CameraLink视频输出接口回环到CameraLink视频输入接口,这样FPGA又接受到了CameraLink的LVDS差分视频信号了,再把这个信号送入CameraLink解码模块,解为RGB视频,最后经过HDMI编码模块输出显示器显示;如此一来,输入和输出都是HDMI视频,却同时验证了CameraLink解码模块和编码模块,却输出效果可通过显示器直观查看,可谓相当精巧的方案

ID:27320720756624203

FPGA小白

FPGA纯verilog编解码CameraLink视频

摘要:本文旨在探讨FPGA纯verilog实现CameraLink视频接收和发送的实现设计方案。由于项目中没有CameraLink相机,但需要验证CameraLink解码模块和编码模块的正确性,本文通过巧妙地设计实验方案来解决这一问题。具体而言,通过采集HDMI输入视频,并经过HDMI解码模块解码为RGB数据后,将其输入CameraLink编码模块,生成CameraLink的LVDS差分视频信号。将该信号通过CameraLink视频输出接口回环到CameraLink视频输入接口,以实现FPGA对CameraLink的LVDS差分视频信号的接收。再将该信号输入CameraLink解码模块,解码为RGB视频,最终通过HDMI编码模块输出到显示器进行观察。通过这种方案,既验证了CameraLink解码模块和编码模块的正确性,又能通过显示器直观查看输出效果。

关键词:FPGA、verilog、CameraLink、编码、解码、HDMI、数据传输

-

引言

CameraLink是一种用于高速视频、图像传输和数据通信的接口标准,广泛应用于工业摄像机等领域。为了验证CameraLink解码模块和编码模块的正确性,本文通过FPGA纯verilog编写实现了CameraLink视频接收和发送的设计方案。 -

设计思路

由于项目中没有CameraLink相机,为了验证解码模块和编码模块的正确性,本文采用了以下设计思路:

2.1 HDMI输入视频采集

首先,通过FPGA采集HDMI输入视频信号,将其作为验证的来源。这里使用HDMI解码模块对输入视频进行解码,以获取RGB数据。

2.2 CameraLink编码

将解码后的RGB数据作为输入,通过纯verilog编写的CameraLink编码模块进行编码,生成CameraLink的LVDS差分视频信号。

2.3 CameraLink视频输出回环

将编码后的CameraLink信号通过CameraLink视频输出接口回环到CameraLink视频输入接口。这样,FPGA又接收到了CameraLink的LVDS差分视频信号。

2.4 CameraLink解码

将回环接收到的CameraLink信号输入纯verilog编写的CameraLink解码模块,解码为RGB视频。

2.5 HDMI编码和输出

最后,将解码后的RGB视频通过HDMI编码模块进行编码,并输出到显示器进行观察。通过显示器直观查看输出效果,用于验证CameraLink解码模块和编码模块的正确性。

-

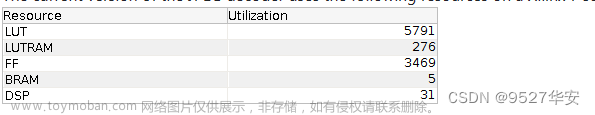

设计实现

通过上述设计思路,我们可以实现FPGA纯verilog编解码CameraLink视频的设计方案。具体的设计实现细节可以参考[1]。 -

结论

本文详细描述了FPGA纯verilog实现CameraLink视频接收和发送的设计方案。通过巧妙地设计实验方案,我们成功地验证了CameraLink解码模块和编码模块的正确性。采用HDMI输入视频作为验证来源,经过解码、编码、回环、再解码等步骤,最终通过显示器直观观察输出效果。本设计方案具有精巧和实用的特点,可以作为类似项目的参考和借鉴。

参考文献:

[1] 详细设计文档参考链接:http: t.csdn.cn W6ag5文章来源:https://www.toymoban.com/news/detail-855071.html

【相关代码 程序地址】: http://nodep.cn/720756624203.html文章来源地址https://www.toymoban.com/news/detail-855071.html

到了这里,关于《FPGA纯Verilog设计实现CameraLink视频编解码验证方案》的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!