介绍

逐级进位加法器就是将上一位的输出作为下一位的进位输入,依次这样相加。下面以一个8位逐级进位加法器给大家展示。

我增加了电路结构,应该很容易理解吧。

下面我也列举了一位加法器,可以看下。

电路结构

设计文件

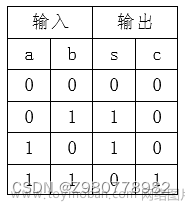

1位加法器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity adder1 is

port (a,b,cin : in std_logic;

sum,s : out std_logic);

end adder1;

--architecture

architecture adder1 of adder1 is

begin

sum <= a xor b xor cin;

s <= (a and b) or (a and cin) or (b and cin);

end adder1;

8位逐级进位加法器

library ieee;

use ieee.std_logic_1164.all;

entity adder2 is

generic (length : integer := 8);

port (a,b : in std_logic_vector(length-1 downto 0);

cin : in std_logic;

s : out std_logic_vector(length-1 downto 0);

output : out std_logic);

end entity;

architecture adder2 of adder2 is

begin

process(cin,a,b)

variable carry :std_logic_vector(length downto 0);

begin

carry(0):=cin;

for i in 0 to length-1 loop

s(i) <= a(i) xor b(i) xor carry(i);

carry(i+1) := (a(i) and b(i)) or (a(i) and carry(i+1)) or (b(i) and carry(i+1));

end loop;

output <= carry(length);

end process;

end architecture;

测试文件

1位加法器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity tb_adder1 is

end tb_adder1;

architecture adder1 of tb_adder1 is

component adder1 is

port (a,b,cin : in std_logic;

sum,s : out std_logic);

end component;

signal a,b,cin,sum,s :std_logic;

begin

dut : adder1

port map (a,b,cin,sum,s);

process

begin

a<='0';

b<='1';

cin<='1';

wait for 10ns;

cin<='0';

wait for 10ns;

a<='1';

b<='1';

wait for 10ns;

end process;

end architecture adder1;

8位逐级进位加法器

library ieee;

use ieee.std_logic_1164.all;

entity tb_adder2 is

generic (length : integer := 8);

end entity;

architecture adder2 of tb_adder2 is

component adder2 is

port (a,b : in std_logic_vector(length-1 downto 0);

cin : in std_logic;

s : out std_logic_vector(length-1 downto 0);

output : out std_logic);

end component adder2;

signal a,b,s : std_logic_vector(length-1 downto 0):= "00000000";

signal cin,output : std_logic := '0';

begin

dut : adder2

port map(

a => a,

b => b,

cin => cin,

s => s,

output => output);

process

begin

a <= "01111000";

b <= "10101100";

cin <= '1';

wait for 20ns;

cin <= '0';

a <= "10011000";

b <= "10100010";

wait for 20ns;

end process;

end architecture;

仿真结果

1位加法器

8位逐级进位加法器

结语

这就是8位逐级进位加法器的全过程了,总体来说还是非常简单的。文章来源:https://www.toymoban.com/news/detail-856341.html

有什么问题欢迎大家留言。文章来源地址https://www.toymoban.com/news/detail-856341.html

到了这里,关于使用FPGA实现逐级进位加法器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA]用Verilog写一个简单三位二进制加法器和减法器](https://imgs.yssmx.com/Uploads/2024/02/761556-1.png)