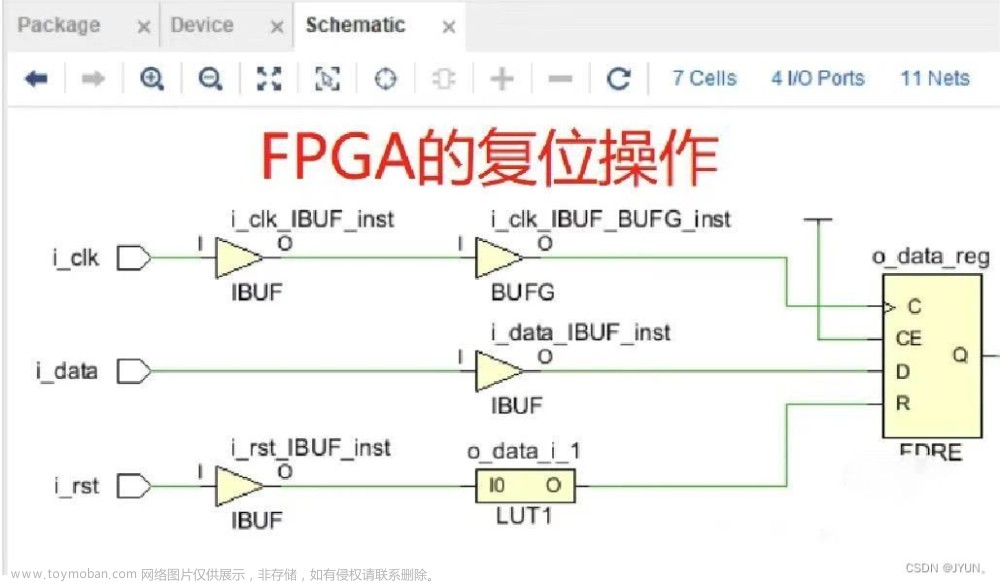

所谓的“同步”、“异步”,指复位的执行与时钟 (CLK)是否同步,可通过敏感列表中是否包含复位信号判断。

同步复位:复位信号和时钟同步,当时钟上升沿检测到复位信号,执行复位操作。——always@(posedge clk)

异步复位:不受时钟影响,只要复位信号有效,就会进行复位。——always@(posedge clk or posedge rst)

异步复位-同步释放

结合同/异步复位各自的优点,一般设计中采用“异步复位-同步释放”方式,即:

1.复位信号的到来是随机的,不与时钟信号的同步;

2.而复位信号释放的时候受到时钟信号的同步;

同步复位的优点

可使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高,确保复位只发生在有效时钟沿:

1.可过滤掉高于时钟频率的rst信号毛刺;

2.有效防止rst信号不满足“Trecovery (recoverytime,恢复时间)”or“Tremoval(removal time消除时间)”而产生的亚稳态;

同步复位的缺点

复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如: 时钟偏移、组合逻辑路径延时、复位延时等因素。

由于Xilinx目标库内的D触发器只有异步复位端口,如采用同步复位,就会耗费更多的逻辑资源 (每次增加一个LUT作为反相器)。

异步复位优点

异步复位优点 (与同步复位缺点相对应来看):

由于大多数的厂商目标库内的触发器都有异步复位端口,可以节约逻辑资源。

异步复位缺点

异步复位缺点(同上,与同步复位优点相对应来看):

1.复位信号容易受到毛刺的影响。

2.复位释放时刻恰在亚稳态窗口内时,不满足Trecovery (recovery time,恢复时间)”or“Tremoval(removal time,消除时间)”而产生的亚稳态

Xilinx复位tips

1.不需要全局复位信号;

2.高电平复位;

3.同步复位或异步复位,同步释放;

4.不需要复位的 bit就不要复位;

AMD XILINX官方授权培训 线下《FPGA工程师》岗前培训班

报名倒计时3天

我们为你提供什么?

1.理论+实验+案例+实践

2.AMD-xilinx官方讲师+985名师督学+企业工程师指导

3.专业教程+量身定制课程+企业应用方案

4.多年培训经验,打造企业定制化人才培养模式

本期课程具体安排

1.阶段一:“F学社”智慧社区--线上理论复习及刷题

——集成电路基础

——部分课程选修(数字电路原理与设计选修、Verilog HDL语言课程选修、EDA系统设计选修)

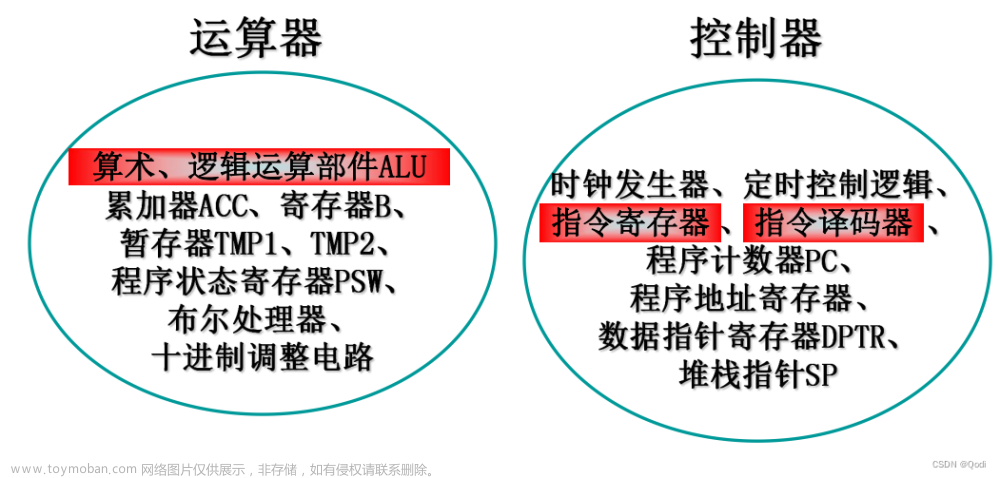

——计算机组成原理

——嵌入式系统

2.阶段二:数字设计基础(线上+线下)

——Xilinx FPGA 架构、开发环境及开发板

——仿真及调试技术

——IP复用技术

——复杂数字系统设计

3.阶段三:高校教师线上直播课程3

——硬件算法

——高层次综合的设计方法

4.阶段四:设计开发进阶

——高级时序约束和分析

——设计优化

——FPGA高级接口设计

——SoC 系统设计基础

——高级SoC系统案例设计

——XILINX 最新器件设计介绍及应用

——FPGA高级应用介绍

最终获得:AMD-XILINX官方证书+企业招聘

不愁找不到工作~文章来源:https://www.toymoban.com/news/detail-856353.html

扫描图片底部二维码即可报名~有任何问题欢迎询问文章来源地址https://www.toymoban.com/news/detail-856353.html

到了这里,关于FPGA的复位操作的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!