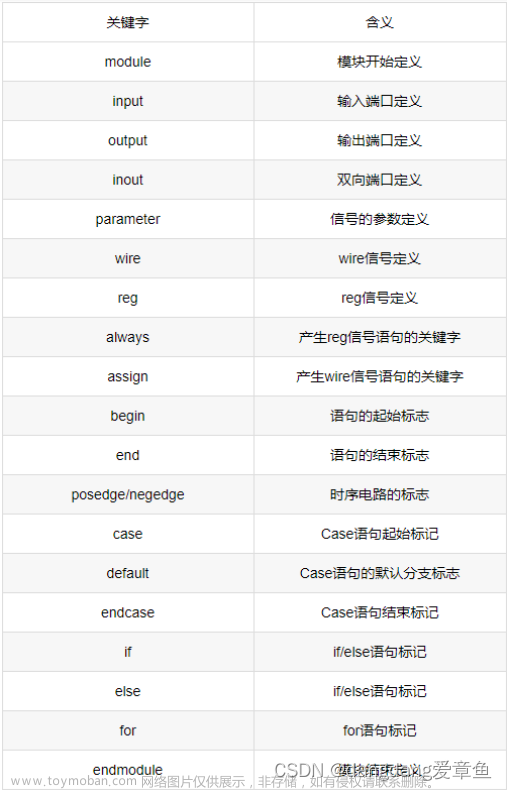

概述:

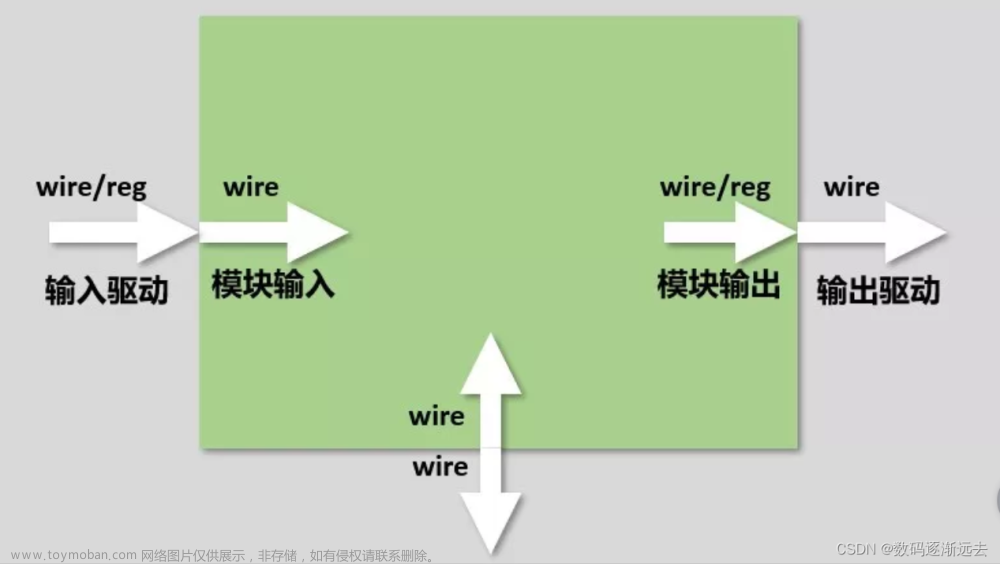

输入输出是模块的端口,寄存器是数据存储介质,线用于把各个电路关联起来,形成一个数据流通通道,进行形成具有具体功能的电路模块。线是信息关联与传递的介质,也是可以称为信息流通的管道。在FPGA中的基本定义为wire,reg,input,output,inout。只有正确的认识到这些基本概念,才能进行正确的开发。

内容

1. 线与寄存器 wire与reg

2. 输入 intput

3. 输出 output

4. 输入输出 inout

1. 线与寄存器 wire与reg

wire与reg简介

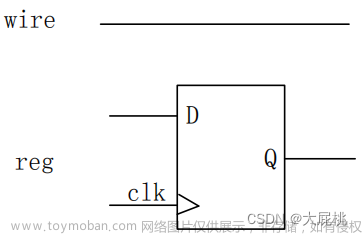

wire 线:金属线,FPGA内部各个端口之间的连接线。它是实物器件,与它相关联的电属性是电位,电流,以及延时时间,线越长,延时时间越长。

作用:

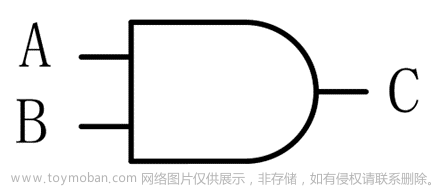

通过assign语句构造组合逻辑电路,赋值语句等。

总线wire, 总线wire可以看成式一维向量,可以把分离的存储数据,或者线按一定顺序排列起来形成总线。

reg 寄存器,FPGA使用触发器或者锁存器来实现,用于存储数据,相当于变量。它的数据可以修改,但是构成寄存器的电路不可以修改,也就相当于地址是固定的。

reg A; 用于存储1一个二进制。

reg [3:0] A1; 一维向量reg用于存储一个多位二进制数

reg [3:0] A2 [15:0]; 二维阵列位,相当于一维整数数组。

注意wire只能在assin语句中赋值;reg只能在awalys语句赋值。

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a,b

);

wire c;

assign c = a&b;

reg A;

reg [3:0] A1;

reg [3:0] A2 [15:0];

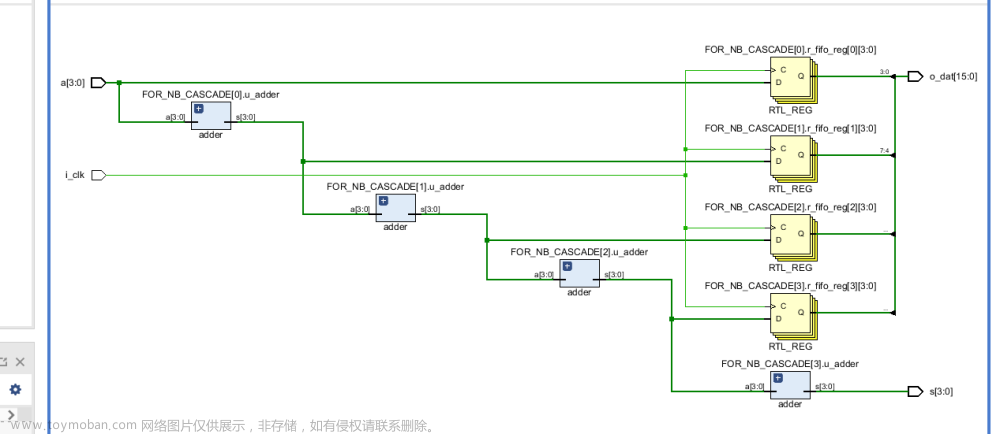

always @(posedge clk ) begin

A<=1'b1;

A1<=4'b0100;

A2[0] <= 4'hf;

A2[15] <= 4'ha;

end

endmodule

2. 输入 intput

简介

输入一般分为时钟输入,复位输入以及数据输入;数据输入又分为1位输入和向量总线输入;

其中时钟输入是模块工作的心脏,模块如果仅仅只是组合逻辑,可以没有时钟。

复位主要是为了同步一下初始状态,使得整个模块从一个预期的初始点开始工作。

数据输入,分为1位输入和总线输入,是输入流入模块的端口。

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a,

input [3:0] b

);

endmodule

3. 输出 output

简介

一个模块对数据进行加工处理后,通过输出通知或者传递信息给外界。工作状态输出,通讯中的信息传递输出,计算中的结果输出等。

输出分类

推挽输出

三态输出

代码

module regtest(

input a,

input en,

output b,

output [1:0] b1,

output c,

output d

);

assign b = ~a;

assign b1 = {~a,a};

assign c = en?a:1'bz; // 三态输出

endmodule

4. 输入输出 inout

总结

1. wire和reg是基础文章来源:https://www.toymoban.com/news/detail-856909.html

2. input和output是最常用的端口文章来源地址https://www.toymoban.com/news/detail-856909.html

到了这里,关于verilog基础语法,wire,reg,input,output,inout的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!