altera fpga ep4cgx22cf19c8,有原理图,PCB图纸,源代码,PCIe二次开发驱动和代码等。

ID:313000681436451614

小明子555

《基于Altera FPGA EP4CGX22CF19C8的硬件开发与PCIe驱动开发》

摘要:本文基于Altera FPGA EP4CGX22CF19C8芯片,探讨了硬件开发和PCIe驱动开发的相关技术。首先介绍了EP4CGX22CF19C8芯片的基本信息和性能特点,然后详细讲解了硬件开发的步骤和相关工具,包括原理图设计、PCB图纸设计和源代码编写。接着,针对PCIe二次开发驱动和代码,本文提供了详细的实现步骤和注意事项。最后,通过实验验证了硬件开发和PCIe驱动开发的可行性和稳定性。

关键词:Altera FPGA EP4CGX22CF19C8、硬件开发、PCIe驱动开发、原理图设计、PCB图纸设计、源代码编写、二次开发驱动、可行性、稳定性

-

引言

近年来,随着FPGA技术的不断发展,越来越多的工程师和开发者开始关注并应用FPGA芯片。Altera作为FPGA领域的一家重要厂商,其EP4CGX22CF19C8芯片具有高性能和灵活性等特点,成为了许多项目的首选。本文旨在介绍基于EP4CGX22CF19C8芯片的硬件开发和PCIe驱动开发的相关技术,为工程师们提供一份实用的指南。 -

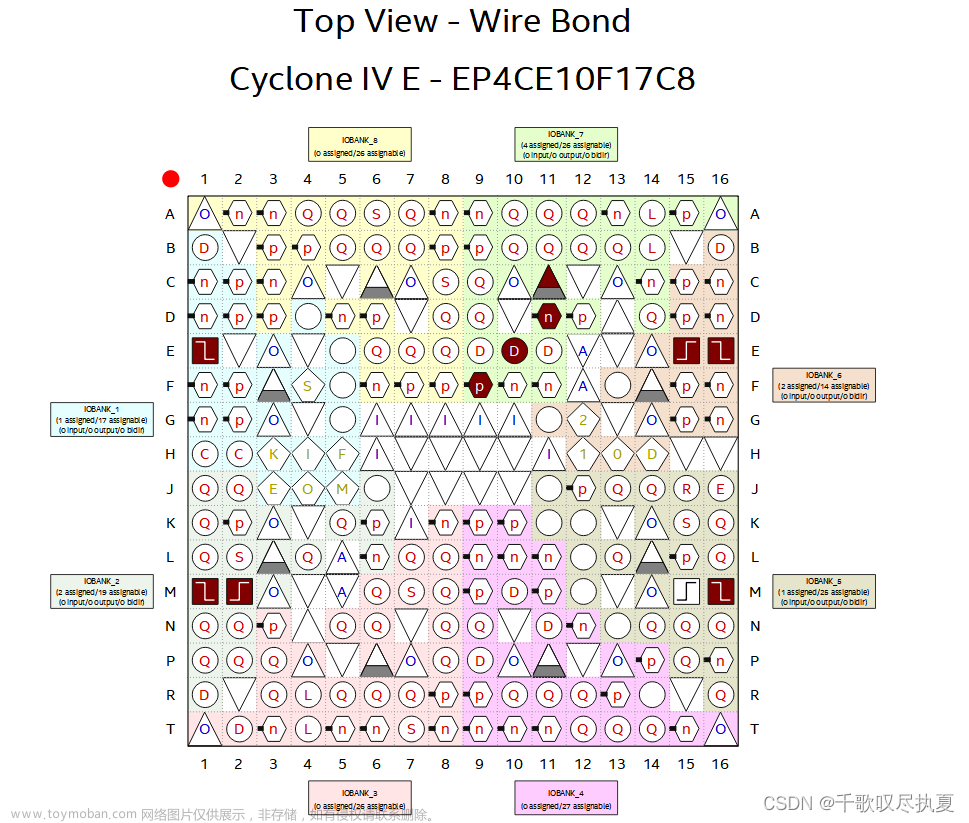

EP4CGX22CF19C8芯片的基本信息和性能特点

EP4CGX22CF19C8芯片是一款高性能的FPGA芯片,具有较大的逻辑单元数量和存储容量。其性能特点主要包括:

- 高时钟频率:EP4CGX22CF19C8芯片具有较高的时钟频率,可以满足复杂应用的需求。

- 丰富的逻辑资源和存储容量:EP4CGX22CF19C8芯片提供了大量的逻辑单元和存储单元,可支持复杂的设计和算法。

- 低功耗设计:EP4CGX22CF19C8芯片采用了低功耗设计,具有较低的动态功耗和静态功耗。

-

硬件开发的步骤和相关工具

硬件开发是基于EP4CGX22CF19C8芯片进行系统设计的关键环节。在硬件开发过程中,需要完成原理图设计、PCB图纸设计和源代码编写等工作。具体步骤如下:

3.1 原理图设计

原理图设计是硬件开发的第一步,通过使用EDA工具绘制原理图,实现系统的功能和连接。在设计过程中,需要考虑输入输出接口、时钟设置和信号传输等因素。

3.2 PCB图纸设计

PCB图纸设计是将原理图转化为实际电路板的过程,需要进行布局和布线设计。在设计过程中,要注意信号完整性、电磁兼容性和散热等问题。

3.3 源代码编写

源代码编写是实现硬件功能的关键,可以使用硬件描述语言(HDL)进行编写。在编写过程中,需要理解EP4CGX22CF19C8芯片的架构和特性,并实现系统功能的逻辑。 -

PCIe二次开发驱动和代码

PCIe是一种高速数据传输接口,常用于计算机和外部设备之间的数据通信。在EP4CGX22CF19C8芯片的硬件开发中,需要进行PCIe驱动的二次开发和代码编写。主要步骤如下:

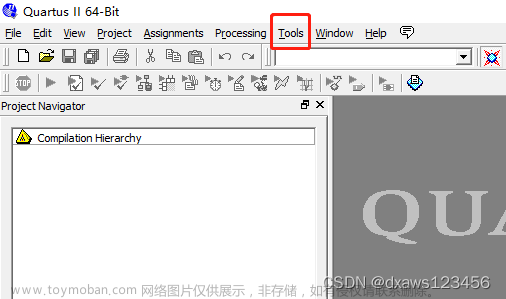

4.1 驱动开发环境的搭建

在进行PCIe驱动开发之前,需要搭建相应的开发环境。包括安装驱动开发工具、配置开发环境和建立开发板连接等。

4.2 驱动开发的实现步骤

驱动开发的实现步骤包括注册设备、分配资源、设置中断处理程序和实现数据传输等。在每个步骤中,需要了解EP4CGX22CF19C8芯片的寄存器和寄存器操作方法,并根据需求进行相应的代码编写。

4.3 注意事项

PCIe驱动开发过程中需要注意的事项包括稳定性测试、错误处理机制、性能优化和兼容性调试等。这些方面的考虑对于保证驱动的可靠性和稳定性至关重要。 -

实验验证与结果分析

为了验证硬件开发和PCIe驱动文章来源:https://www.toymoban.com/news/detail-857278.html

【相关代码 程序地址】: http://nodep.cn/681436451614.html文章来源地址https://www.toymoban.com/news/detail-857278.html

到了这里,关于【技术分享】Altera FPGA EP4CGX22CF19C8详解:原理图、PCB图纸、源代码及PCIe二次开发驱动和代码全解析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!