一、核心思路

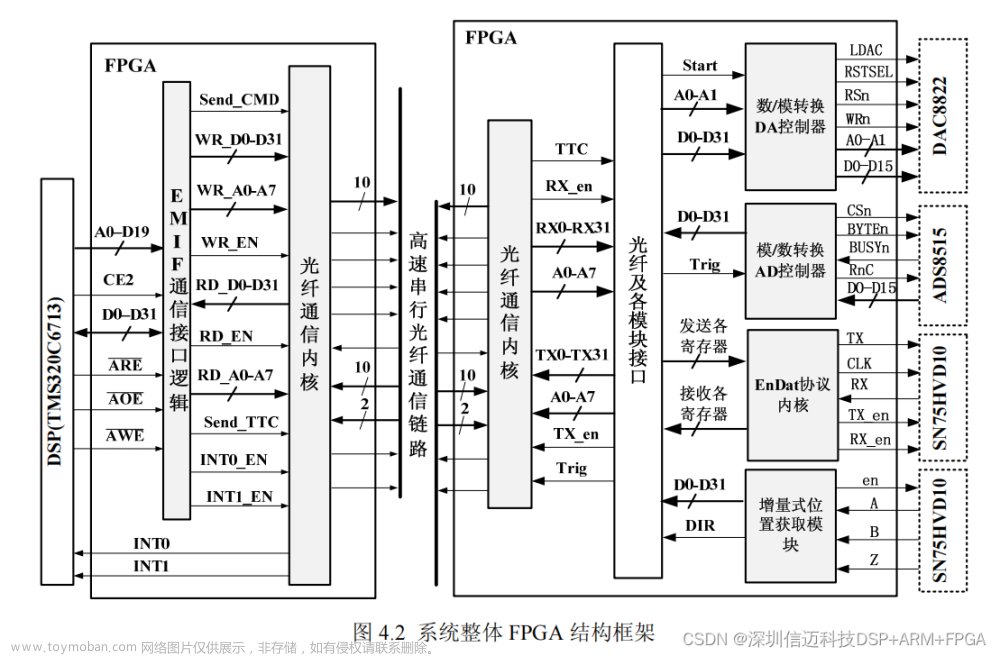

以 FIFO IP 核以及 Verilog 编程设计的数字逻辑模块对JESD204B IP 核输出数据完成接收,处理成驱动设备可读取的数据格式后,送入设计的数字逻辑缓存部分中,通过AXI 总线送入DDR3 SDRAM 中缓存,并由传输部分数字逻辑模块完成缓存深度配置。

介绍设计的具体实现。在数字采集功能配置中对 ADC 时钟及寄存器功能配置,实现JESD204B 接口对数据接收。了解MIG IP 核并根据 DDR3 SDRAM 选型与封装完成参数配置,与缓存部分数字逻辑模块构成 DDR3 SDRAM 控制器模块。掌握 XDMA IP 核 DMA 操作并设置参数,与传输部分数字逻辑模块构成 PCIe 总线控制模块,以基于 XDMA 方式实现的 PCIe 高速数据传输,完成硬件FPGA 与板上CPU 数据传输设计。

对板上 CPU 的 PCIe 驱动程序以及 PC 端上位机软件设计,搭建软硬件测试平台并对设计整体功能进行验证。以 Linux 环境下 PCIe 驱动程序实现数据在 FPGA 与板上 CPU 的传输,采用Qt 完成PC 端上位机。分别对ADC 芯片采集功能配置,缓存功能以及传输功能进行测试验证,对中间传输过程产生的信号以及波形进行说明,验证在高速传输过程中数据没有突发传输错误等情况。

二、设计与仿真

作为完成高速数据采集、转换工作的核心——高速ADC,在雷达、无线通信等领域应用越来越广泛,而通过与外部控制器的数据传输完成 ADC 芯片功能配置也成为了热点问题。串行外设接口(Serial Peripheral Interface,SPI)总线协议是一种高速、全双工的数据通信总线,其在芯片中管脚仅占4 条线,即减少了芯片管脚,也易于PCB 的布局。正是凭借着占用信号线少,传输速度快,准确性高等优势,SPI 成为高速ADC 开发的主流趋势。

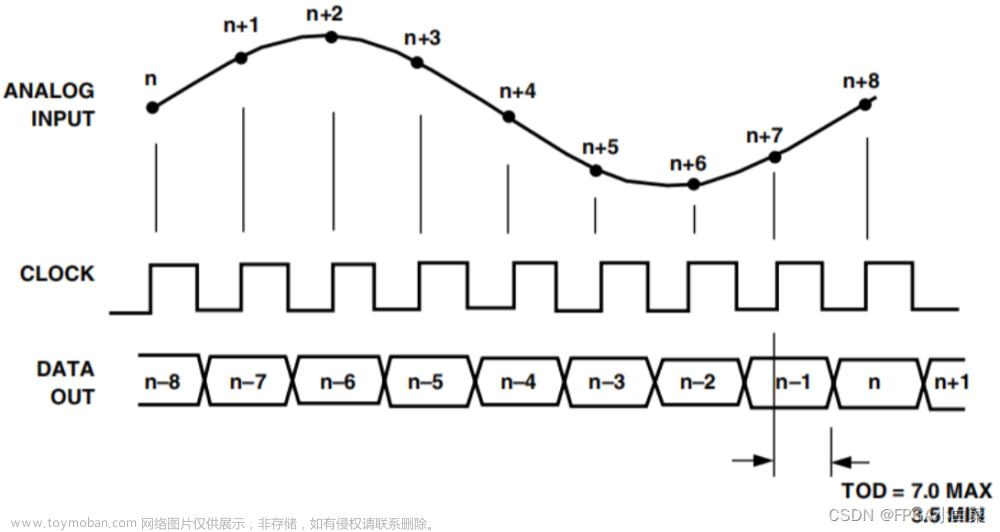

目前市面上大部分高速ADC 芯片都内嵌专用的 SPI 配置接口,对ADC 内部的控制寄存器进行读、写操作可以通过配置其 SPI 接口实现,从而应对不同情况下 ADC 芯片的使用。本文设计中,为满足高速数据采集需求,选用ADS54J60 芯片完成模数转换,该芯片具有 SPI 配置接口且支持 JESD204B 串行接口。在数据采集功能配置部分中,通过配置 SPI 接口电路完成 ADC 芯片功能配置,实现模数转换以及JESD204B 高速数据采集接口对数据接收,再由 FIFO IP 以及数字逻辑模块处理数据后,送至DDR3 SDRAM 控制器模块。

在完成 MIG IP 核运行参数配置后,还需在硬件的基础上对每个物理接口设计 I/O 接口,根据硬件电路图设置I/O 接口

通过AXI Interconnect IP 将缓存逻辑以及 DMA(Direct Memory Access)控制器两个 AXI 内存映射主设备连接到 MIG 内存映射从设备中,具体配置包括主设备、从设备接口数量选择,本设计中分别设为 2、1;对主设备、从设备接口Register Slice 与Data FIFO 功能进行配置,Register Slice 用于时序收敛,但会造成数据输出延迟一个周期,Data FIFO 实现数据缓存,从设备接口使能Register Slice 以及Data FIFO,数据缓存深度为512 位,主设备接口仅使能Register Slice;在高级选项配置中可以设置从设备接口优先级,本文中采用平行优先级,以轮询的方式处理端口请求。文章来源:https://www.toymoban.com/news/detail-857347.html

文章来源地址https://www.toymoban.com/news/detail-857347.html

文章来源地址https://www.toymoban.com/news/detail-857347.html

到了这里,关于FPGA 高速数据采集传输毕业论文【附仿真】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!