FPGA底层架构——FPGA六大组成部分

FPGA底层资源

- 可编程输入输出单元(IOB)

- 可编程逻辑单元(CLB)

- 时钟管理单元(DCM)

- 嵌入块状RAM(BRAM)

- 布线资源

- 内嵌的专用硬件模块(硬IP,硬核)

- 内嵌的底层功能单元(软IP,软核)

- 补充(DSP48、PLL资源、乘法器资源等,)

最重要的部分<big><font color="red">可编程输入输出单元、可编程逻辑单元、布线资源</font></big>

1.IO、IOB(可编程输入输出单元,Input/Output Block)

FPGA的IOB是输入/输出块(Input/Output Block)的简称,它是FPGA内部实现复杂逻辑的关键部分,负责处理输入输出信号。IOB内部包含了一系列的逻辑单元,用以完成信号的缓冲、驱动、映射等功能。

在Xilinx的FPGA中,IOB内部结构可以简化为以下几个主要部分:

- 输入缓冲器(Input Buffers):用于提高信号的鲁棒性和减少信号的噪声干扰。

- 输出驱动器(Output Drivers):负责将FPGA内部逻辑单元的信号驱动到IOB外部。

- 串并转换(Serial-to-Parallel and Parallel-to-Serial Converters):用于实现信号的串并转换,以适应不同位宽的信号传输。

- 控制逻辑(Control Logic):负责处理IOB的各种配置和功能控制信号。

FPGA IO命名与Bank划分

FPGA I/O之差分信号

2.CLB(可编程逻辑单元,Configurable Logic Block)

在FPGA中,CLB是实现逻辑功能的基本单元,一个CLB由2个slice组成,slice可以分成以下的两类:SliceM(Memory)和SliceL(Logic)。这两种slice的区别在于它们的LUT不同。

- SLICEM(M:Memory):其内部的LUT可以读也可以写,可以实现移位寄存器和64bit的DRAM等存储功能,还可以实现基本的查找表逻辑。

- SLICEL(L:Logic): 其内部的LUT只可以读,只能实现基本的查找表逻辑。

SliceL和SliceM内部都包含

-

4个6输入查找表(LUT6)

- FPGA原理与结构(2)——查找表LUT(Look_Up_Table)

- FPGA原理与结构(5)——移位寄存器(Shift Registers)

- FPGA原理与结构(6)——分布式RAM(Distributed RAM,DRAM)

- RAM分类及实现

-

3个数据选择器(MUX)

- FPGA原理与结构(4)——数据选择器MUX(Multiplexers)

-

1个进位链(Carry Chain)

进位链CARRY在FPGA中本质上就是解决加减法进位问题的元器件

- FPGA原理与结构(7)——进位链CARRY

-

8个触发器(Flip-Flop)

- FPGA原理与结构(3)——存储单元(Storage Elements)

CLB的sliceM中LUT形成的RAM可以同步写异步读,而BRAM形成的RAM只能同步写同步读。**

补充:

- 单端口RAM:只有一个读写口,就是只有一组数据线和地址线,就是读和写都是通过这个口来访问 RAM,但是同一个时刻只能访问一个,要么是读,要么是写。

- 伪双端口 RAM :指的是有两个读写端口,但是一个端口只能读,一个端口只能写,伪双端口 RAM 一般叫 TP RAM。一般 FIFO 内部例化的都是伪双端口 RAM。

- 真双端口RAM:真双端口 RAM 指的是有两个读写端口,每个端口都可以独立发起读或者写。

3.时钟管理单元

-

区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。时钟资源

-

FPGA时钟资源主要有三大类:时钟管理单元、时钟IO、时钟布线资源。

-

时钟管理模块:不同厂家及型号的FPGA中的时钟管理资源会有一些差异,主要功能是对时钟的频率、占空比、相位等功能的管理。例如:PLL,DLL,DCM,MMCM(混合模式时钟管理器)等。

-

Clock 10:时钟IO,FPGA的时钟I0分布在不同的区域。像xiinx的时钟IO分为MRCC(全局时钟pin)和SRCC(局部时钟pin)。

-

Clock Routing Source:时钟布线资源含有时钟线以及时钟缓冲器,数量上会比前两者多;含全局时钟网络(GCLK)和局部时钟网络(RCLK)的时钟线及缓冲(BUFG,BUFR等)。

PLL

MMCM

-

DCM(数字时钟管理器,Digital Clock Manager)

通过 FPGA 芯片提供的DCM 功能, 可灵活地控制时钟频率、相位转换和时钟脉冲相位差。

- FPGA时钟资源1

- FPGA时钟资源2

zynq

器件延时 T C O T_{CO} TCO大概0.2ns

建立时间大概0.01ns

保持时间大概0.12ns

3.1 时序约束

-

为什么要时序约束?——综合工具是以时序约束为驱动的进行布局布线的策略,即时序约束是综合工具进行综合的参考点

-

同步系统的要求

- 寄存器(触发器)的建立时间满足要求

- 那么什么时候建立时间不满足呢——建立时间裕量不够, T l o g i c T_logic Tlogic大,即组合逻辑处理时间过长

- 寄存器(触发器)的保持时间满足要求

- 跨时钟域设计

- 数据源端由寄存器产生,并且数据到下一个寄存器几乎是直接相连(出现的概率较低)

- 数据的发起沿和数据的捕获沿相差一个CLK

- 寄存器(触发器)的建立时间满足要求

-

时序约束1——数据传输模型

通过vivado官方例程IP学习时序约束

4.块状RAM(BRAM,block ram)

- FPGA BRAM

Xilinx 7系列FPGA的bram最小大小为36Kb,可配置为两个18Kb,也可级联成更大的RAM,另外每个bram内封有寄存器,可作为输出缓冲,好处便是不需要利用CLB的触发器(这样会加大延时

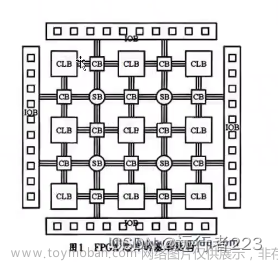

5.布线资源

FPGA中的布局布线资源主要包括三部分:CB、SB和行列连线。布线资源的目的是为了能够让位于不同位置的逻辑资源块、时钟处理单元、BLOCK RAM、DSP和接口模块等资源能够相互通信,从而协调合作,完成所需功能。FPGA中的布线资源,就好比绘制PCB板时的连线资源一样,虽然器件A和器件B的位置和连接关系没有任何改变,但很可能因为周边电路的布局、布线的一些变化,使得前后两次A、B之间的连线形态发生很大的变化。因此,与采用固定长度的金属线将所有宏单元连接在一起的CPLD不同,FPGA中任意两点之间的线延迟是无法预测的,必须等到布局、布线完成之后才能确定。这也是为什么在FPGA的开发中,时序约束和时序分析这两样工作是必不可少的。

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。主要分为四类:全局布线资源、长线资源、短线资源、分布式布线资源。

6.DSP核

Xilinx FPGA中可用的最复杂的计算块是下图所示的DSP48块文章来源:https://www.toymoban.com/news/detail-858538.html

DSP48块是嵌入FPGA结构中的算术逻辑单元(ALU),由三个不同的块组成的链。DSP48中的计算链包含一个加/减单元,连接到一个乘法器,再连接到最后的加/减/累加引擎。这条链允许单个DSP48单元实现如下形式的函数:P=Bx(A+D)+C or P+=Bx(A+D)文章来源地址https://www.toymoban.com/news/detail-858538.html

到了这里,关于FPGA底层架构——FPGA六大组成部分的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!