一、插件安装&配置

安装Verilog-HDL/SystemVerilog/Bluespec SystemVerilog插件实现语法高亮、定义跳转、代码检错

配置方法:

1.打开配置界面.

2.在Ctags路径选项的框内填入ctags.exe所在路径.(实现定义跳转功能)

3.语法检查选项,检查器选择modelsim,并选择Modelsim的工作库所在位置.(实现语法检查)

工作库的建立方法(以vivado联合modelsim仿真为例)

1.打开vivado,如图所示选择Compile Simulation.

2.仿真器选择ModeiSim的,选择常见的器件家族,建立存在工作库的文件目录并填入,选择modelsim的win64文件夹作为modelsim仿真器所在目录,勾选Compile Xilinx IP,最后点击compile即可生成相应工作库(注:此处等待时间较长).

安装Verilog Highlight实现变量高亮.

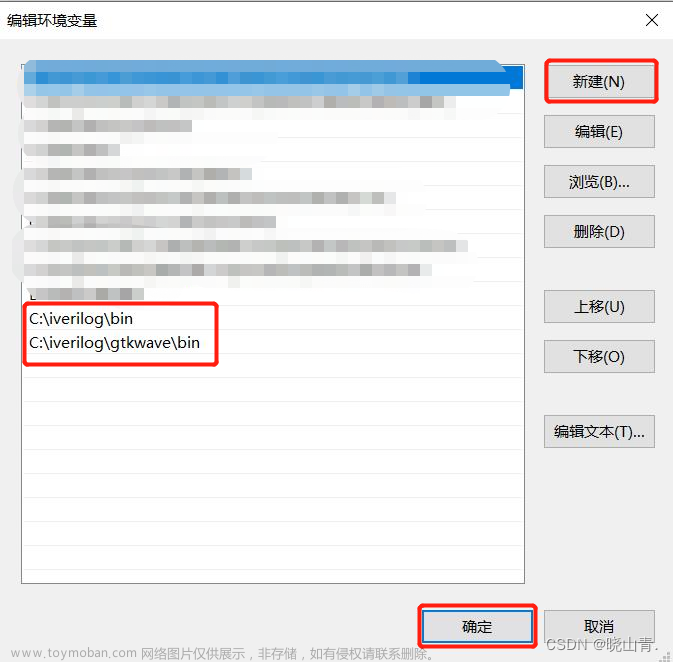

二、在VSCode中编译&打开Modelsim仿真

1.编译

在VSCode中打开源文件所在目录,编写完设计文件和仿真文件后,按住ctrl+`打开终端,输入vlog *.v 编译该工作目录下的全部.v文件.(也可以输入vlog xxx.v文件单独编译对应的.v文件).

编译完成后,错误和警告信息在终端中可见.

2.打开modelsim仿真

在终端中输入vsim xxx.v(xxx.v为对应tb文件名).

随后弹出modelsim.

3.Modelsim中的界面设置

1.将每个界面打开到最大;

2.工具栏处右键,只保留此三项,然后移动对应工具组位置,调整至自己喜欢的状态.

4.Modelsim基础操作

1.展开work,找到对应的tb文件,右键Simulate.

2.在sim中,找到被例化的文件,右键添加到波形.

3.进入波形界面,右键时间,选择Grid那项.

4.取消勾线网格设置,时间单位根据需要设置.

注:3、4操作过以后,操作结果会适用于之后新建的modelsim工程中.文章来源:https://www.toymoban.com/news/detail-860431.html

5.点击图示按钮简化变量名,变量位置可拖动调整.

6.选择相关变量后可点击调整属性

一般常调整:进制选项,取消进制前置位的显示,设置颜色和调整高度.

选择完毕后点击Apply,再点击OK关闭窗口即可.

7.输入仿真时间(如1000ms),点击开始仿真

8.观测仿真结果,点击下图所示按键能切换到一个比较舒服的观测比例.

观测示例:

在观测的过程中,可以锁住对应光标的位置作为标记,然后点击+后重新生成一个自由光标,自由光标生成多了可以点击-删除. 文章来源地址https://www.toymoban.com/news/detail-860431.html

文章来源地址https://www.toymoban.com/news/detail-860431.html

到了这里,关于如何在VSCode中优雅地书写Verilog的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!