设计可运行的最高频率

Fmax可通过时序报告计算得出。在Vivado中,可通过命令report_timing_summary生成时序报告.WNS越大越好.

输入到输出的时钟周期数

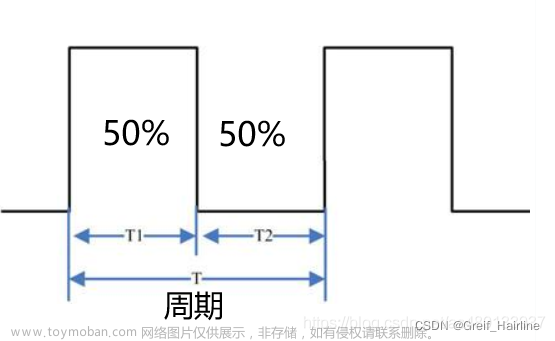

输入到输出的延迟通常用时钟周期个数来表示,称为Latency,该指标也反映了设计的流水级数。Latency越小越好。但Latency小意味着流水级数低,这可能会导致Fmax降低。

可通过命令xilinx::designutils::report_failfast查看资源利用率的指导值和实际值

将图1-48中的信息提取出来形成表。表中LUTRAM表示分布式RAM,SRL表示用LUT实现的移位寄存器。根据此表,我们可以在设计初期进行芯片选型。需要注意的是,Block RAM、UltraRAM和DSP48三者资源利用率都不能超过80%,若超过了80%,则要保证三者平均利用率低于80%。

RAMB"是指FPGA中的RAMB(Random Access Memory Block),是一种用于存储数据的可编程存储块。RAMB通常是FPGA中的内部存储资源,用于实现存储器功能,如RAM(随机存取存储器)或ROM(只读存储器)

UltraRAM是FPGA(现场可编程门阵列)中的一种高性能存储资源。它是Xilinx FPGA架构中的一部分,与传统的Block RAM(BRAM)不同,UltraRAM提供了更高容量的存储和更灵活的配置选项。

UltraRAM可以用于存储大容量的数据,例如存储大型数组、缓存数据、图像、视频等。它还可以用于实现更复杂的算法和应用,如神经网络模型、高性能计算等。与传统的Block RAM相比,UltraRAM具有更高的存储密度和更低的时延,这使得它在某些应用中能够提供更好的性能和效率。文章来源:https://www.toymoban.com/news/detail-860881.html

资源利用率和功耗

在Vivado下,可通过命令report_power生成当前设计的功耗报告 文章来源地址https://www.toymoban.com/news/detail-860881.html

文章来源地址https://www.toymoban.com/news/detail-860881.html

到了这里,关于【FPGA】优化设计指南(二):性能指标的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!